# **Communication Characteristics** and Hybrid MPI/OpenMP Parallel Programming on Clusters of Multi-core SMP Nodes

Georg Hager, Erlangen Regional Computing Center (RRZE) Gabriele Jost, Texas Advanced Computing Center (TACC) Rolf Rabenseifner, High Performance Computing Center Stuttgart (HLRS) Neil Stringfellow, Swiss National Supercomputing Centre (CSCS), presenter

> **Cray User Group** Atlanta, GA, May 4-7, 2009

### Aspects & Outline

- High Performance Computing (HPC) systems

- Always hierarchical hardware design

- Programming models on hierarchical hardware

- Mismatch problems

- Programming models are not suited for hierarchical hardware

- Performance opportunities with MPI+OpenMP hybrid programming

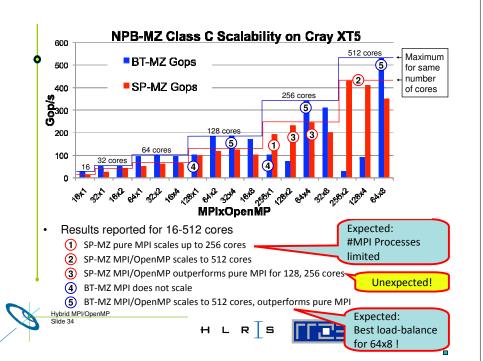

- NPB BT/SP-MZ benchmark results on Cray XT5

- Optimization always requires knowledge about the hardware

- ... and appropriate runtime support

- It's a little more complicated than make; mpirun

# **High Performance Computing (HPC) systems** → hierarchical hardware design!

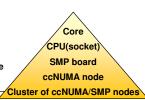

- Efficient programming of clusters of SMP nodes SMP nodes:

- · Dual/multi core CPUs

- · Multi CPU shared memory

- Multi CPU ccNUMA

- · Any mixture with shared memory programming model

- Hardware range

- · mini-cluster with dual-core CPUs

- · large constellations with large SMP nodes

- ... with several sockets (CPUs) per SMP node

- ... with several cores per socket

- → Hierarchical system layout

SMP nodes

Node Interconnect

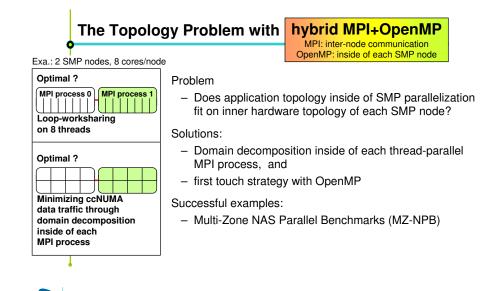

- Hybrid MPI/OpenMP programming seems natural

- · MPI between the nodes

- · OpenMP inside of each SMP node

# Which is the best programming model?

Hybrid MPI/OpenMP

- Which programming model is fastest?

- MPI everywhere?

Fully hybrid MPI & OpenMP?

Something between? (Mixed model)

Lore: hybrid programming slower than pure MPI - Why?

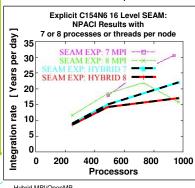

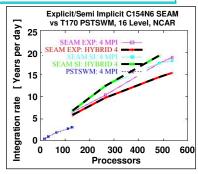

### **Example from SC**

- Pure MPI versus Hybrid MPI+OpenMP (Masteronly)

- What's better?

- → What does it depend on?

Figures: Richard D. Loft, Stephen J. Thomas, John M. Dennis:

Terascale Spectral Element Dynamical Core for Atmospheric General Circulation Models. Proceedings of SC2001, Denver, USA, Nov. 2001. http://www.sc2001.org/papers/pap.pap189.pdf Fig. 9 and 10.

# **Parallel Programming Models on Hybrid Platforms**

pure MPI one MPI process on each CPU

hybrid MPI+OpenMP MPI: inter-node communication OpenMP: inside of each SMP node OpenMP only distributed virtual shared memory

No overlap of Comm. + Comp. MPI only outside of parallel regions of the numerical application code

Overlapping Comm. + Comp. MPI communication by one or a few threads while other threads are computing

"Masteronly" mode

This can get ugly...

R. Rabenseifner, G. Wellein: Communication and Optimization Aspects of Parallel Programming Models on Hybrid Architectures. International Journal of High Performance Computing Applications 17(1), 49-62 (2003).

### Pure MPI

pure MPI one MPI process on each CPU

#### Advantages

- No modifications on existing MPI codes

- MPI library need not to support multiple threads

#### Major problems

- Does MPI library internally use different protocols?

- · Network communication between the nodes

- · Shared memory inside of the SMP nodes

- Usually true today, but see later

- Does application topology fit on hardware topology?

- MPI-communication inside of SMP nodes unnecessary?

# **Hybrid Masteronly**

#### Masteronly MPI only outside of parallel regions

#### **Advantages**

- No message passing inside SMP nodes

- No intra-node topology problem (but watch thread placement)

for (iteration ....)

#pragma omp parallel numerical code /\*end omp parallel \*/

/\* on master thread only \*/ MPI\_Send (original data to halo areas in other SMP nodes) MPI Recv (halo data from the neighbors) } /\*end for loop

Hybrid MPI/OpenMP

**Major Problems**

- All other threads are sleeping while master thread communicates!

- Inter-node bandwidth saturation?

- As of MPI 2.1, MPI lib must support at least MPI THREAD FUNNELED (there is no MPI THREAD MASTERONLY)

### **Overlapping Communication and Computation**

MPI communication by one or a few threads while other threads are computing

```

if (my thread rank < ...) {

MPI Send/Recv....

i.e., communicate all halo data

} else {

Execute those parts of the application

that do not need halo data

(on non-communicating threads)

Execute those parts of the application

that need halo data

(on all threads)

```

Core

CPU(socket)

SMP board

ccNUMA node

Cluster of ccNUMA/SMP nodes

### Pure OpenMP (on the cluster)

#### OpenMP only distributed virtual shared memory

- Distributed shared virtual memory system needed

- Must support clusters of SMP nodes

- e.g., Intel<sup>®</sup> Cluster OpenMP

- Shared memory parallel inside of SMP nodes

- Communication of modified parts of pages at OpenMP flush (part of each OpenMP barrier)

i.e., the OpenMP memory and parallelization model is prepared for clusters!

pure MPI one MPI process

on each CPU

# **Mismatch Problems**

- None of the programming models fits to the hierarchical hardware (cluster of SMP nodes)

- Several mismatch problems

- → following slides

- Benefit through hybrid programming

- → opportunities, see last section

- Quantitative implications

- → depends on the application

| Examples:                                 | No.1 | No.2 |

|-------------------------------------------|------|------|

| Benefit through hybrid (see next section) | 30%  | 10%  |

| Loss by mismatch problems                 | -10% | -25% |

| Total                                     | +20% | -15% |

In most cases: Both categories!

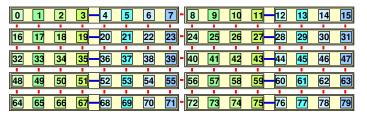

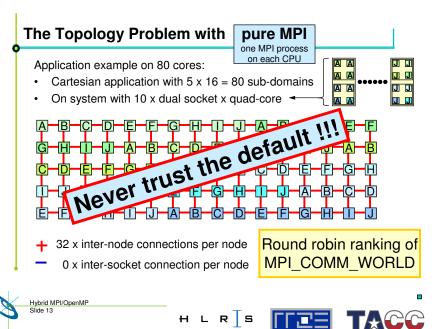

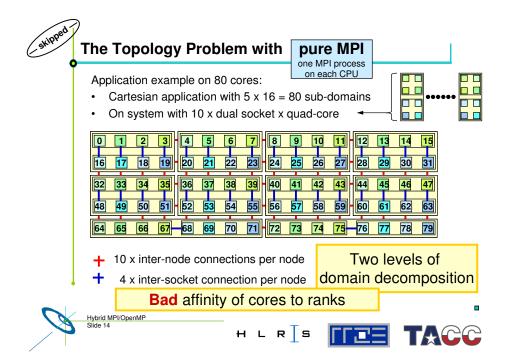

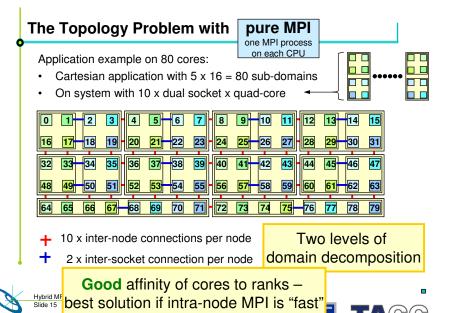

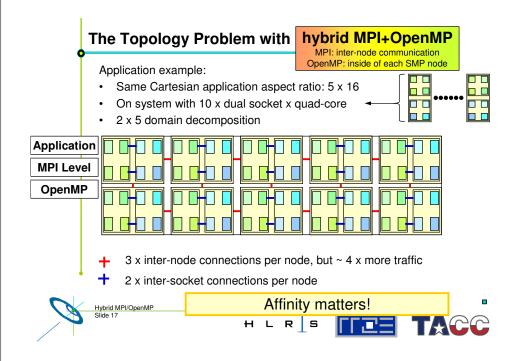

Application example on 80 cores:

Cartesian application with  $5 \times 16 = 80$  sub-domains

On system with 10 x dual socket x quad-core

+ 17 x inter-node connections per node

1 x inter-socket connection per node

Sequential ranking of MPI COMM WORLD

Does it matter?

Hybrid MPI/OpenMP

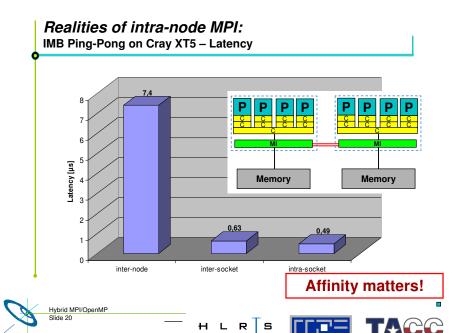

### Intra-node communication issues

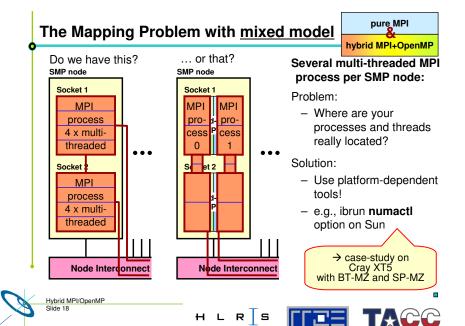

pure MPI

Mixed model

several multi-threaded MP

processes per SMP node)

#### Problem:

If several MPI processes on each SMP node

→ unnecessary (and inefficient?) intra-node communication

#### Remarks:

- MPI library must use appropriate fabrics / protocol for intra-node communication

- Intra-node bandwidth/latency probably much better than inter-node

- → problem may be small

- MPI implementation may cause unnecessary data copying

- → waste of memory bandwidth

Quality aspects of the MPI library

#### Realities of intra-node MPI: IMB Ping-Pong on Cray XT5 - Bandwidth 3000 Shared cache 2500 advantage Bandwidth [MBytes/s] ◆ XT5 inter-node □-□ inter-socket O intra-socket Between two cores of one socket Between two nodes via interconnect fabric Between two sockets 500 of one node (cache effects eliminated) **Affinity matters!** 10<sup>4</sup> 10<sup>5</sup> 10 Message length [bytes] HLRTS Memory Memory

## Overlapping Communication and Computation

MPI communication by one or a few threads while other threads are computing

#### Three problems:

- · the application problem:

- one must separate application into:

- · code that can run before the halo data is received

- · code that needs halo data

### → very hard to do !!!

- the thread-rank problem:

- comm. / comp. via thread-rank

- cannot use work-sharing directives

- → loss of major OpenMP support (see next slide)

- · the load balancing problem

#### MPI communication by one or a few threads while other threads are computing Subteams #pragma omp parallel proposal #pragma omp single onthreads(0) for OpenMP 3.x? or OpenMP 4.x MPI Send/Recv.... Barbara Chapman et al.: Toward Enhancing OpenMP's #pragma omp for onthreads(1: omp\_get\_numthreads()-1) Work-Sharing Directives. In proceedings, W.E. Nagel et { /\* work without halo information \*/ al. (Eds.): Euro-Par 2006. } /\* barrier at the end is only inside of the subteam \*/ LNCS 4128, pp. 645-654, 2006. #pragma omp barrier #pragma omp for Tasking (OpenMP 3.0) for (.....) - works only if app { /\* work based on halo information \*/ can cope with dynamic scheduling

**Overlapping Communication and Computation**

Hybrid MPI and OpenMP Parallel Programming. SC08 Tutorial M09

} /\*end omp parallel \*/

### OpenMP: Additional Overhead & Pitfalls

- Using OpenMP

- → may prohibit compiler optimization

- → may cause significant loss of computational performance

- Thread fork / join, implicit barriers (see next slide)

- · On ccNUMA SMP nodes:

- E.g. in the masteronly scheme:

- · One thread produces data

- · Master thread sends the data with MPI

- → data may be communicated between NUMA domains

- · Amdahl's law for each level of parallelism

- Using MPI-parallel application libraries?

- → Are they prepared for hybrid?

Hybrid MPI/OpenMP Slide 25

#### Perf. model: $P(N,T) = \frac{..}{N/T/P(N/T,1) + t_{\text{overhead}}}$ OpenMP overhead on Cray XT5 Nomenclature: 5000 r T=1 outer T=2 outer 1S T=2 outer 2S 1S/2S [MFlops/sec] 3000 T=4 outer 1S 1-/2-socket T=4 outer 2S T=8 outer T=8 outer nowait inner T=8 overhead=157 ns parallel on · · · T=8 overhead=780 ns Performance [I inner loop outer parallel on outer loop nowait 1000 no barrier on for Loop length loop **Affinity matters!** H L R S Memory Memory

### **OpenMP Overhead**

- As with intra-node MPI, OpenMP loop start overhead varies with the mutual position of threads in a team

- Possible variations

- Intra-socket vs. inter-socket

- Different overhead for "parallel for" vs. plain "for"

- If one multi-threaded MPI process spans multiple sockets,

- · ... are neighboring threads on neighboring cores?

- · ... or are threads distributed "round-robin" across cores?

- Test benchmark: Vector triad

```

#pragma omp parallel

for(int j=0; j < NITER; j++) {

#pragma omp (parallel) for (nowait)

for(i=0; i < N; ++i)

a[i]=b[i]+c[i]*d[i];

if(OBSCURE)

dummy(a,b,c,d);</pre>

Look at array s

```

Look at performance for small array sizes!

### No silver bullet

Hybrid MPI/OpenMP

- The analyzed programming models do **not** fit on hybrid architectures

- whether drawbacks are minor or major

- > depends on applications' needs

- But there are major opportunities → see below

- · In the NPB-MZ case studies

- We tried to use an optimal parallel environment

- for pure MPI

- · for hybrid MPI+OpenMP

- i.e., the developers of the MZ codes and we tried to minimize the mismatch problems by using appropriate system tools

# Opportunities of hybrid parallelization (MPI & OpenMP)

**Overview**

- Nested Parallelism

- → Outer loop with MPI / inner loop with OpenMP

- Load-Balancing

- → Using OpenMP dynamic and guided worksharing

- Memory consumption

- → Significant reduction of replicated data on MPI level

- Chances, if MPI speedup is limited due to "algorithmic" problems

- → Significantly reduced number of MPI processes

- → OpenMP threading makes each process "faster", even if code is already Amdahl-limited

Hybrid MPI/OpenMP

#### **Nested Parallelism**

- Example NPB: BT-MZ (Block tridiagonal simulated CFD application)

- Outer loop:

- · limited number of zones

- → limited parallelism

- zones with different workload

Sum of workload of one zone

speedup < Sum of workload of all zones

- Inner loop:

- OpenMP parallelized (static schedule)

- · Not suitable for distributed memory parallelization

- Principles:

- Limited parallelism on outer level

- Additional inner level of parallelism

- Inner level not suitable for MPI

- Inner level may be suitable for static OpenMP worksharing

### **Benchmark Characteristics**

- · Aggregate sizes and zones:

- Class B: 304 x 208 x 17 grid points,

- Class C: 480 x 320 x 28 grid points, 256 zones

- Class D: 1632 x 1216 x 34 grid points, 1024 zones

- Class E: 4224 x 3456 x 92 grid points, 4096 zones

- BT-MZ:

#### **Block tridiagonal simulated CFD application**

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

### Scalar Pentadiagonal simulated CFD application

- Size of zones identical

- · no load-balancing required

MPI level: Pure MPI should perform best

Expectations:

Pure MPI:

Load-balancing

problems!

Good candidate

for

MPI+OpenMP

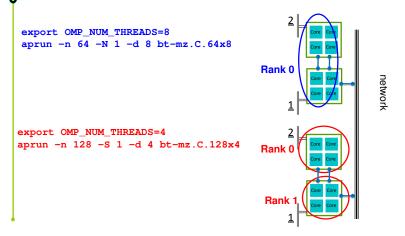

# **Cray XT5 Experiments**

- Results obtained by the courtesy of the HPCMO Program and the Engineer Research and Development Center Major Shared Resource Center, Vicksburg, MS (<a href="http://www.erdc.hpc.mil/index">http://www.erdc.hpc.mil/index</a>)

- Cray XT5 is located at the Arctic Region Supercomputing Center (ARSC)

- 432- Cray XT5 compute nodes with

- 32 GB of shared memory per node (4 GB per core)

- 2 quad core 2.3 GHz AMD Opteron processors per node.

- 1 Seastar2+ Interconnect Module per node.

- Cray Seastar2+ Interconnect between all compute and login nodes

- Compilation:

- Cray ftn compiler based on PGI pgf90 7.2.2

- ftn -fastsse -tp barcelona-64 -r8 -mp=nonuma

- Execution:

- MPICH based MPI-2

- export OMP\_NUM\_THREADS={8,4,2,1}

- aprun -n NPROCS -N 1 -d 8 ./a.out

- aprun -n NPROCS -S {1,2,4} -d {4,2,1} ./a.out

# **Cray XT5 Process Placement**

Slide 33

### **Conclusions & outlook**

- Future High Performance Computing (HPC)

- → always hierarchical hardware design

- Mismatches and chances with current MPI based programming models

- → Some new features are needed

- → Some optimizations can be done best by the application itself

#### MPI + OpenMP:

- Often hard to solve the mismatch problems

- May be a significant chance for performance

- →(huge) amount of work

- Optimization always requires knowledge on the hardware:

- → Qualitative and quantitative information is needed

- → through a standardized interface?

- ... and don't forget the usual OpenMP pitfalls

- → Fork/join, barriers, NUMA placement