© Rolf Rabenseifner: Parallel Programming Models on Hybrid Systems.

© Rolf Rabenseifner: Parallel Programming Models on Hybrid Systems.

© Rolf Rabenseifner: Parallel Programming Models on Hybrid Systems.

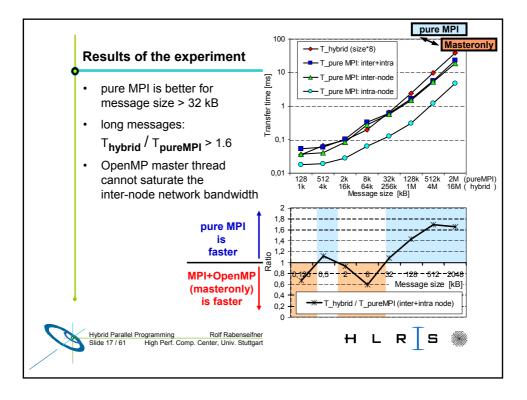

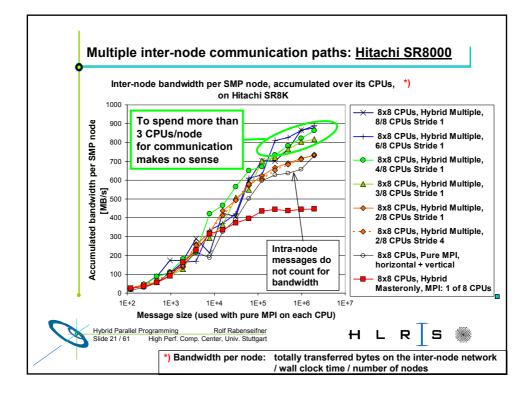

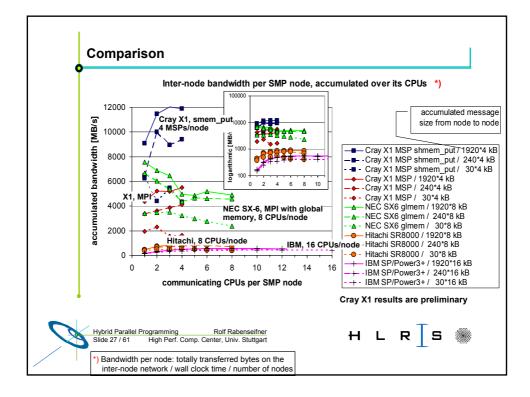

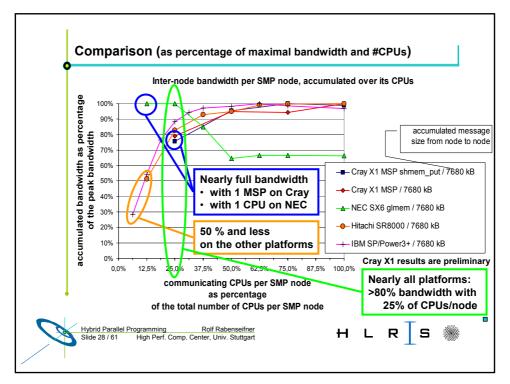

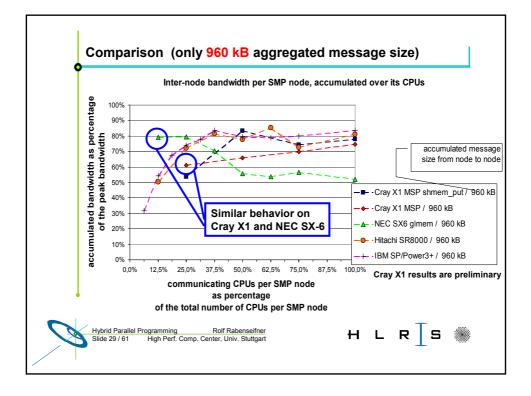

| Comparing inter-node bandwidth with CPU performance                                 |                                              |                                          |                                                   |                                          | *) Bandwidth per node:<br>totally transferred bytes on the network<br>/ number of nodes / wall clock time |                                                  |                                                                        |                                     |

|-------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|---------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|-------------------------------------|

| All values:<br>aggregated over one<br>SMP nodes. *)<br>mess. size: 16 MB<br>*) 2 MB | Master<br>-only,<br>inter-<br>node<br>[GB/s] | pure<br>MPI,<br>inter-<br>node<br>[GB/s] | Master-<br>only bw /<br>max.<br>intra-<br>node bw | pure<br>MPI,<br>intra-<br>node<br>[GB/s] | memo-<br>ry<br>band-<br>width<br>[GB/s]                                                                   | Peak &<br>Linpack<br>perfor-<br>mance<br>Gflop/s | max.inter<br>-node bw<br>/ peak &<br><i>Linpack</i><br>perf.<br>B/Flop | nodes*CPUs                          |

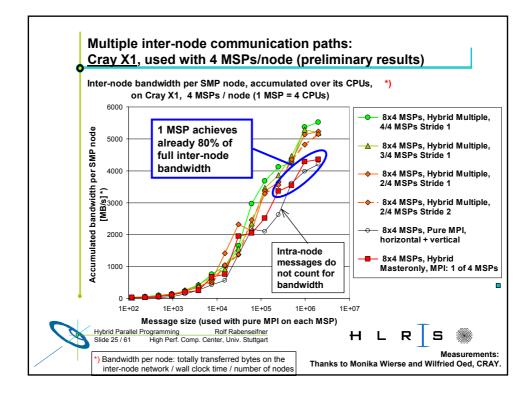

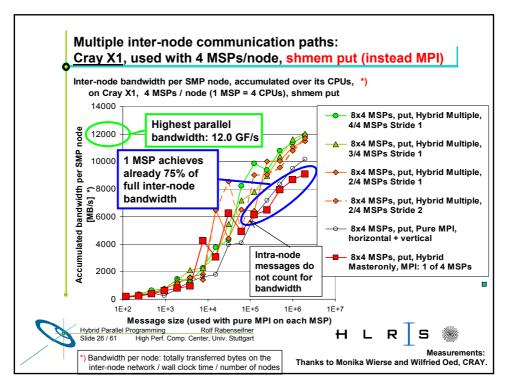

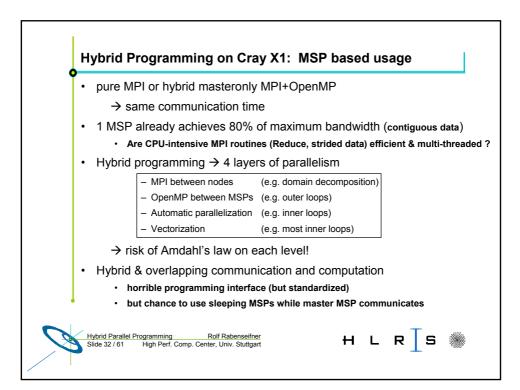

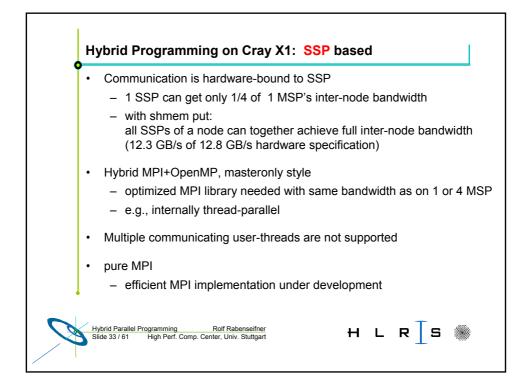

| Cray X1,shmem_put<br>preliminary results                                            | 9.27                                         | 12.34                                    | 75 %                                              | 33.0                                     | 136                                                                                                       | <b>51.2</b><br>45.03                             | <b>0.241</b><br>0.274                                                  | 8 * 4 MSPs                          |

| Cray X1, MPI<br>preliminary results                                                 | 4.52                                         | 5.52                                     | 82 %                                              | 19.5                                     | 136                                                                                                       | <b>51.2</b><br>45.03                             | 0.108<br>0.123                                                         | 8 * 4 MSPs                          |

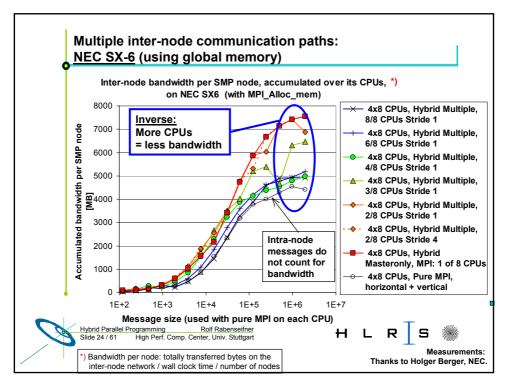

| NEC SX-6<br>global memory                                                           | 7.56                                         | 4.98                                     | 100 %                                             | 78.7<br>93.7 <sup>+</sup> )              | 256                                                                                                       | <b>64</b><br>61.83                               | 0.118<br>0.122                                                         | 4 * 8 CPUs                          |

| NEC SX-5Be<br>local memory                                                          | 2.27                                         | 2.50<br>a)                               | 91 %                                              | 35.1                                     | 512                                                                                                       | <b>64</b><br>60.50                               | <b>0.039</b><br>0.041                                                  | <b>2 *16 CPUs</b><br>a) only with 8 |

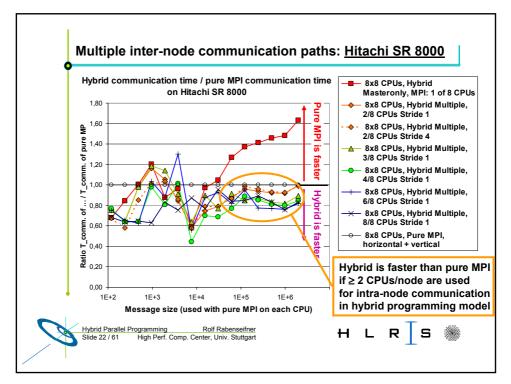

| Hitachi SR8000                                                                      | 0.45                                         | 0.91                                     | <b>49</b> %                                       | 5.0                                      | 32 store<br>32 load                                                                                       | <b>8</b><br>6.82                                 | 0.114<br>0.133                                                         | 8 * 8 CPUs                          |

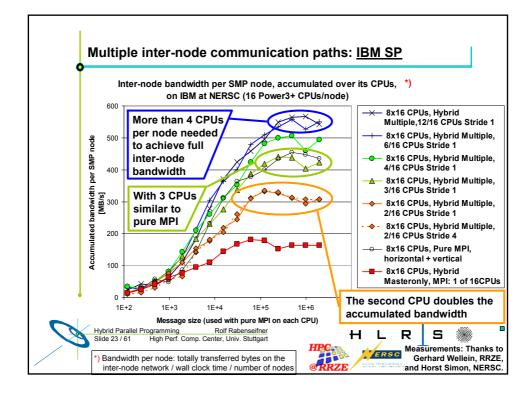

| IBM SP Power3+                                                                      | 0.16                                         | 0.57*)                                   | 28 %                                              | 2.0                                      | 16                                                                                                        | <b>24</b><br>14.27                               | <b>0.023</b><br>0.040                                                  | 8 *16 CPUs                          |

| SGI O3000, 600MHz                                                                   | 0.43*)                                       | 1.74*)                                   | 25 %                                              | 1.73+)                                   |                                                                                                           | <b>4.8</b><br>3.64                               | 0.363<br>0.478                                                         | 16 *4 CPUs                          |

| SUN-fire (prelimi.)                                                                 | 0.15                                         | 0.85                                     | 18 %                                              | 1.68                                     |                                                                                                           |                                                  |                                                                        | 4 *24 CPUs                          |

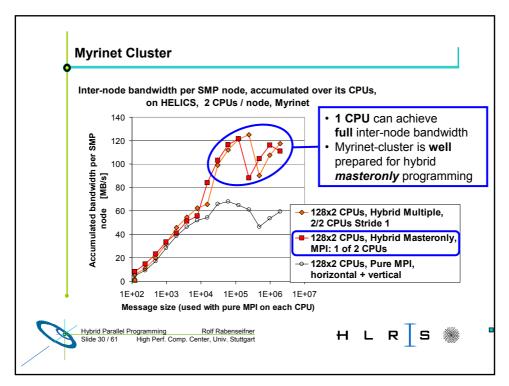

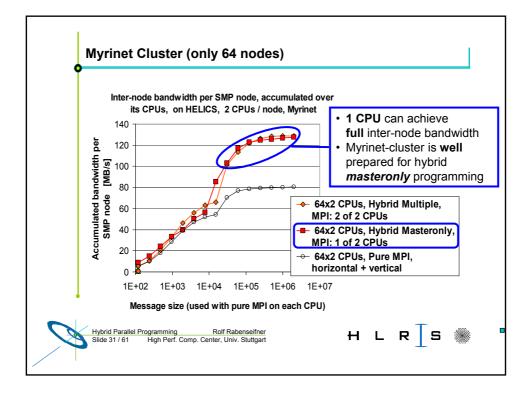

| HELICS Dual-PC<br>cluster with Myrinet                                              | 0.118 *)                                     | 0.119<br>⁺)                              | 100 %                                             | 0.104<br>*)                              |                                                                                                           | <b>2.80</b><br>1.61                              | <b>0.043</b><br>0.074                                                  | 128 *2 CPUs                         |

© Rolf Rabenseifner: **Parallel Programming Models on Hybrid Systems**. HLRS Result and Review Workshop, Oct. 6–7, 2003, HLRS, Stuttgart, Germany. Page 21