# Hybrid Parallel Programming: Performance Problems and Chances on Cray X1, NEC SX-6 and Other Platforms

Rolf Rabenseifner rabenseifner@hlrs.de

University of Stuttgart, High Performance Computing Center Stuttgart (HLRS) www.hlrs.de

#### **CUG SUMMIT 2003**

May 12-16, Columbus, Ohio, USA

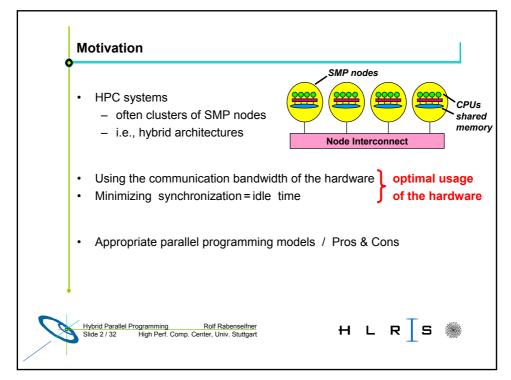

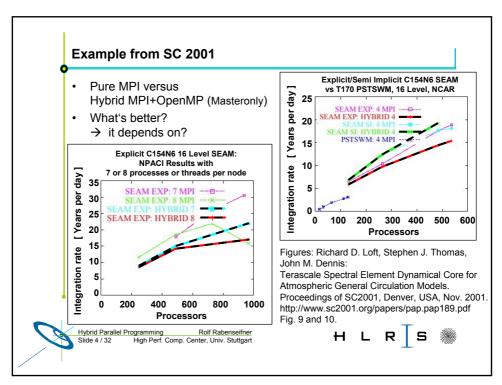

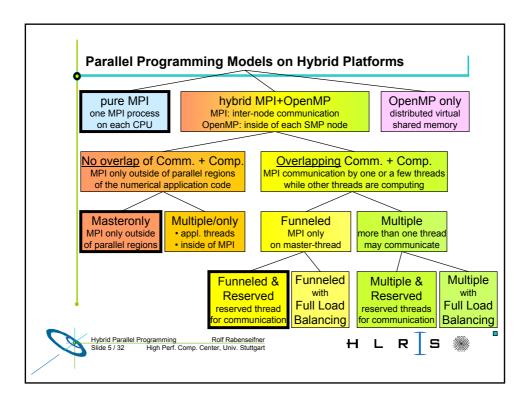

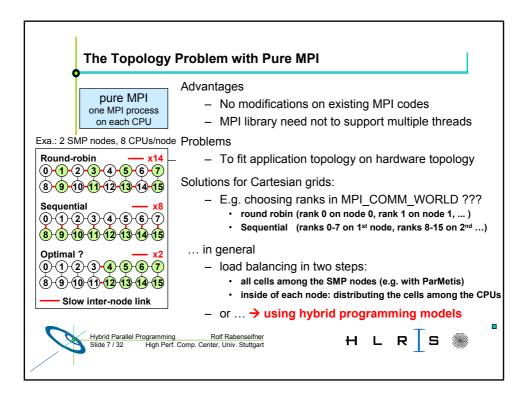

## Major Programming models on hybrid systems

- Pure MPI (one MPI process on each CPU)

- Hybrid MPI+OpenMP

- shared memory OpenMP

- distributed memory MPI

via node interconnect

- · Other: Virtual shared memory systems, HPF, ...

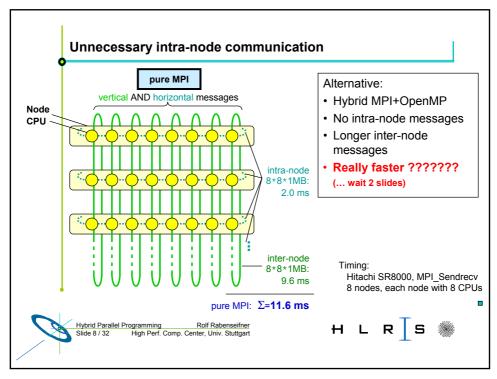

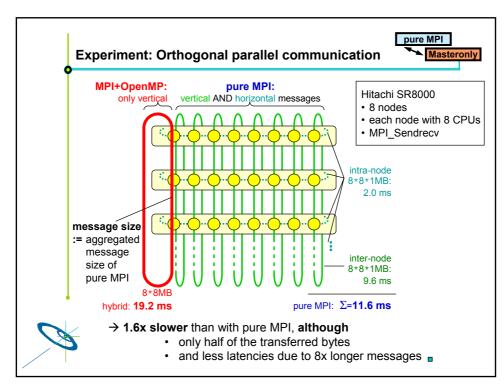

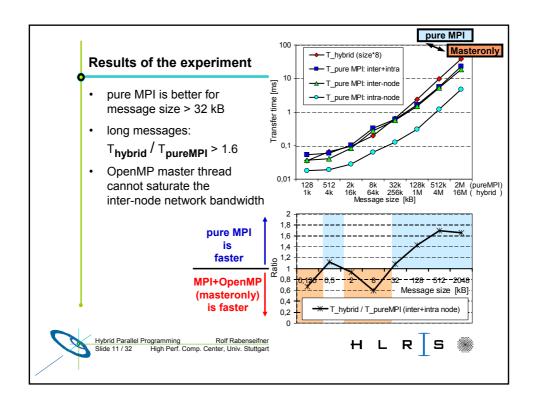

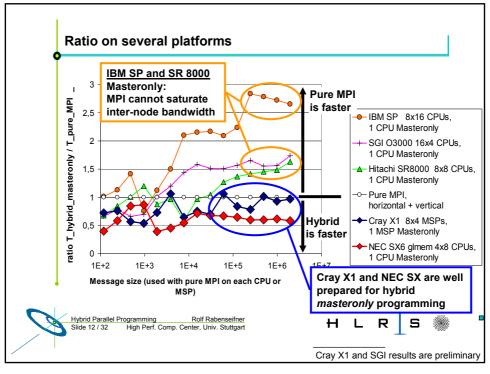

- Often hybrid programming (MPI+OpenMP) slower than pure MPI

- why?

#### **Mismatch Problems**

Topology problem [with pure MPI]

• Unnecessary intra-node communication [with pure MPI]

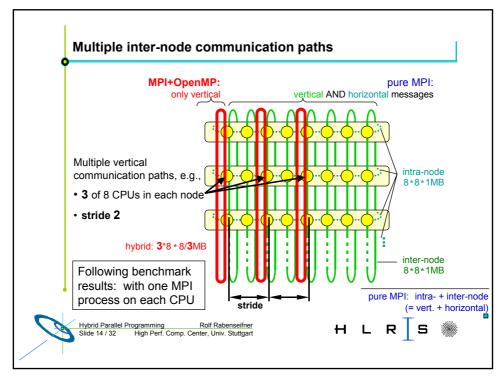

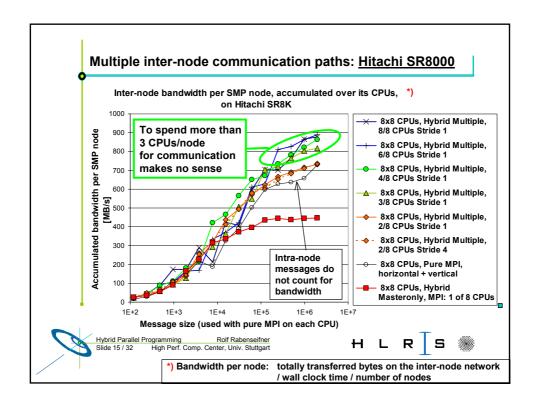

• Inter-node bandwidth problem [with hybrid MPI+OpenMP]

Sleeping threads and saturation problem [with pure MPI]

• Additional OpenMP overhead [with hybrid MPI+OpenMP]

Thread startup / join

Cache flush (data source thread – communicating thread – sync. → flush)

Overlapping communication and computation [with hybrid MPI+OpenMP]

an application problem → separation of local or halo-based code

a programming problem → thread-ranks-based vs. OpenMP work-sharing

- a load balancing problem, if only some threads communicate / compute

#### no silver bullet

# Programming Models on Hybrid Platforms: Hybrid Masteronly

Masteronly MPI only outside of parallel regions

#### Advantages

- No message passing inside of the SMP nodes

- No topology problem

# for (iteration ....) {

#pragma omp parallel

numerical code

/\*end omp parallel \*/

/\* on master thread only \*/

MPI\_Send (original data

to halo areas

in other SMP nodes)

MPI\_Recv (halo data

from the neighbors)

} /\*end for loop

#### **Problems**

MPI-lib must support MPI\_THREAD\_FUNNELED

#### Disadvantages

- do we get full inter-node bandwidth? ... next slide

- all other threads are sleeping while master thread communicates

- →Reason for implementing overlapping of communication & computation

Hybrid Parallel Programming Rolf Rabenseifner

Slide 9 / 32 High Perf. Comp. Center, Univ. Stuttgart

#### **Possible Reasons**

- Hardware:

- is one CPU able to saturate the inter-node network?

- · Software:

- internal MPI buffering may cause additional memory traffic

memory bandwidth may be the real restricting factor?

- → Let's look at parallel bandwidth results

## The sleeping-threads and the saturation problem

- · Masteronly:

- all other threads are sleeping while master thread calls MPI

- → wasting CPU time

- → → → wasting plenty of CPU time if master thread cannot saturate the inter-node network

- Pure MPI:

- all threads communicate,

but already 1-3 threads could saturate the network

wasting CPU time

- Overlapping communication and computation

#### Overlapping Communication and Computation

MPI communication by one or a few threads while other threads are computing

- the application problem:

- one must separate application into:

- · code that can run before the halo data is received

- · code that needs halo data

#### → very hard to do !!!

- the thread-rank problem:

- comm. / comp. via thread-rank

- cannot use work-sharing directives

- → loss of major **OpenMP support**

- the load balancing problem

```

if (my_thread_rank < 1) {

MPI_Send/Recv....

} else {

my_range = (high-low-1) / (num_threads-1) + 1;

my_low = low + (my_thread_rank+1)*my_range;

my_high=high+ (my_thread_rank+1+1)*my_range;

my_high = max(high, my_high)

for (i=my_low; i<my_high; i++) {

}

```

Hybrid Parallel Programming Rolf Rabenseifner

Slide 25 / 32 High Perf. Comp. Center, Univ. Stuttgart

H L R S 🆠

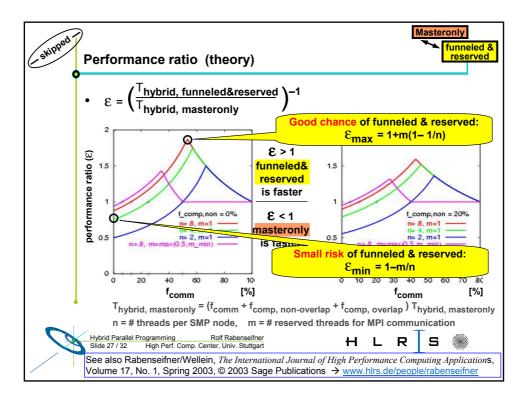

## Overlapping communication and computation (cont'd)

- the load balancing problem:

- some threads communicate, others not

- balance work on both types of threads

- strategies:

Funneled & Reserved for communi.

Multiple & Reserved reserved thread reserved threads for communic.

- reservation of one a fixed amount of threads (or portion of a thread) for communication

- see example last slide: 1 thread was reserved for communication

- → a good chance !!! ... see next slide

Funneled with

Full Load Balancing

Multiple with Full Load Balancing

very hard to do !!!

Hybrid Parallel Programming Rolf Rabenseifner High Perf. Comp. Center, Univ. Stuttgart

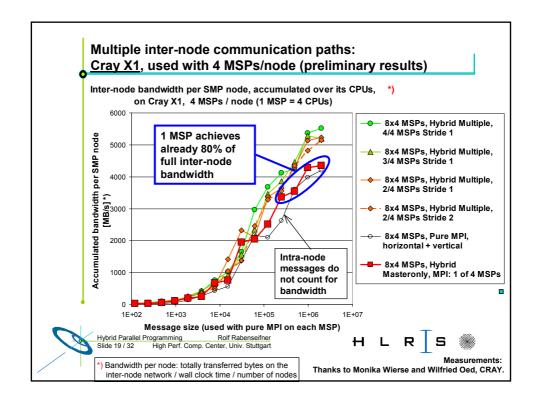

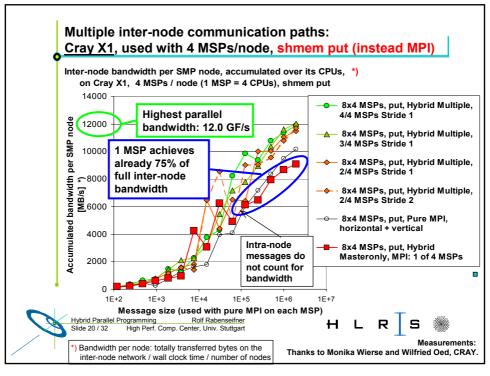

# Hybrid Programming on Cray X1: MSP based usage

- · pure MPI or hybrid masteronly MPI+OpenMP

- → same communication time

- 1 MSP already achieves 80% of maximum bandwidth (contiguous data)

- · Are CPU-intensive MPI routines (Reduce, strided data) efficient & multi-threaded ?

- Hybrid programming → 4 layers of parallelism

- MPI between nodes (e.g. domain decomposition)

- OpenMP between MSPs (e.g. outer loops)

- Automatic parallelization (e.g. inner loops)

- Vectorization (e.g. most inner loops)

- → risk of Amdahl's law on each level!

- Hybrid & overlapping communication and computation

- horrible programming interface (but standardized)

- · but chance to use sleeping MSPs while master MSP communicates

#### Hybrid Programming on Cray X1: SSP based

- · Communication is hardware-bound to SSP

- 1 SSP can get only 1/4 of 1 MSP's inter-node bandwidth

- with shmem put:

all SSPs of a node can together achieve full inter-node bandwidth (12.3 GB/s of 12.8 GB/s hardware specification)

- Hybrid MPI+OpenMP, masteronly style

- optimized MPI library needed with same bandwidth as on 1 or 4 MSP

- e.g., internally thread-parallel

- · Multiple communicating user-threads are not supported

- · pure MPI

Hybrid Parallel Programming

- efficient MPI implementation under development

Hybrid Parallel Programming Rolf Rabenseifner Slide 29 / 32 High Perf. Comp. Center, Univ. Stuttgart

H L R S

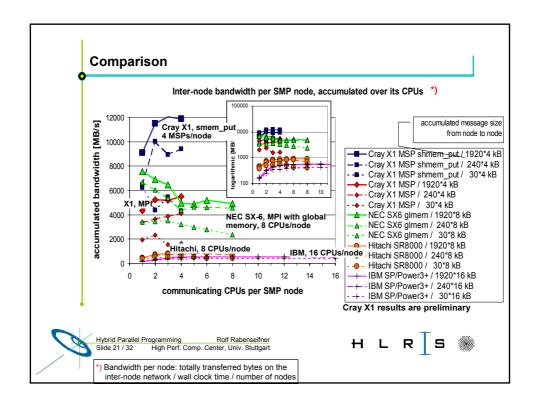

# Comparing inter-node bandwidth with peak CPU performance

| All values:<br>aggregated over<br>one SMP nodes. *)<br>mess. size: 16 MB<br>+) 2 MB | Master<br>-only,<br>inter-<br>node<br>[GB/s] | pure<br>MPI,<br>inter-<br>node<br>[GB/s] | Master-<br>only bw<br>/ max.<br>intra-<br>node bw | pure<br>MPI,<br>intra-<br>node<br>[GB/s] | memo<br>-ry<br>band-<br>width<br>[GB/s] | Peak<br>perfor-<br>mance<br>Gflop/s | max.<br>inter-<br>node bw<br>/ peak<br>perf.<br>B/Flop | nodes*CPUs                   |

|-------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|---------------------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------|--------------------------------------------------------|------------------------------|

| Cray X1,shmem_put preliminary results                                               | 9.27                                         | 12.34                                    | 75 %                                              | 33.0                                     | 136                                     | 51.2                                | 0.241                                                  | 8 * 4 MSPs                   |

| Cray X1, MPI preliminary results                                                    | 4.52                                         | 5.52                                     | 82 %                                              | 19.5                                     | 136                                     | 51.2                                | 0.108                                                  | 8 * 4 MSPs                   |

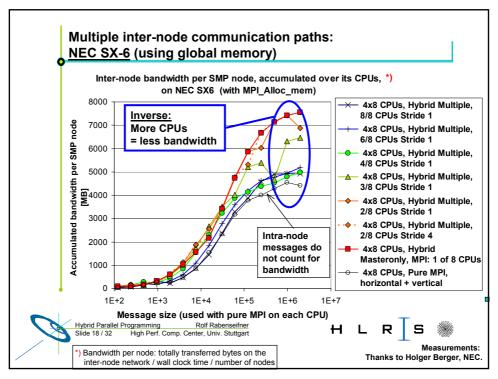

| NEC SX-6<br>global memory                                                           | 7.56                                         | 4.98                                     | 100 %                                             | 78.7<br>93.7 <b>†)</b>                   | 256                                     | 64                                  | 0.118                                                  | 4 * 8 CPUs                   |

| NEC SX-5Be local memory                                                             | 2.27                                         | <b>2.50</b> a)                           | 91 %                                              | 35.1                                     | 512                                     | 64                                  | 0.039                                                  | 2 *16 CPUs<br>a) only with 8 |

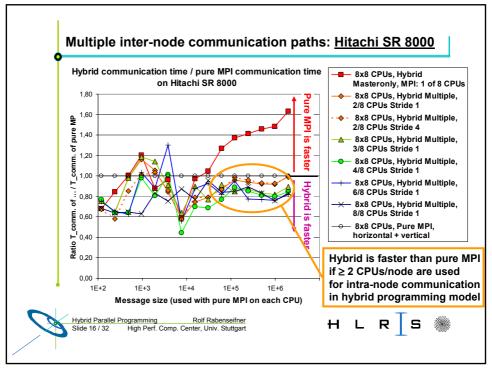

| Hitachi SR8000                                                                      | 0.45                                         | 0.91                                     | 49 %                                              | 5.0                                      | 32 store<br>32 load                     | 8                                   | 0.114                                                  | 8 * 8 CPUs                   |

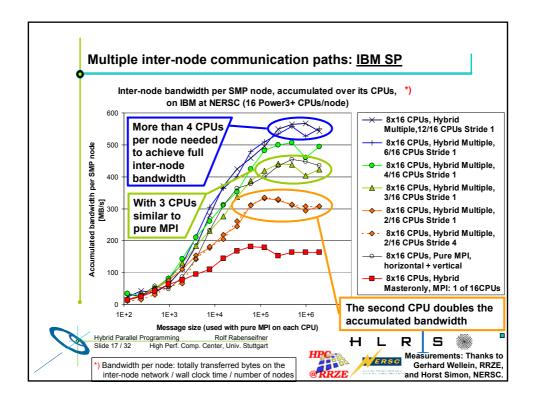

| IBM SP Power3+                                                                      | 0.16                                         | 0.57+)                                   | 28 %                                              | 2.0                                      | 16                                      | 24                                  | 0.023                                                  | 8 *16 CPUs                   |

| SGI Origin 3000 preliminary results                                                 | 0.10                                         | 0.30 <sup>+</sup> )                      | 33 %                                              | 0.39 <b>*)</b>                           | 3.2                                     | 4.8                                 | 0.063                                                  | 16 *4 CPUs                   |

| SUN-fire (prelimi.)                                                                 | 0.15                                         | 0.85                                     | 18 %                                              | 1.68                                     |                                         |                                     |                                                        | 4 *24 CPUs                   |

\*) Bandwidth per node: totally transferred bytes on the network / wall clock time / number of nodes

Н

Rolf Rabenseifner

High Perf. Comp. Center, Univ. Stuttgart

## **Acknowledgements**

- I want to thank

- Gerhard Wellein, RRZE

- Monika Wierse, Wilfried Oed, and Tom Goozen, CRAY

- Holger Berger, NEC

- Gabriele Jost, NASA

- Dieter an Mey, RZ Aachen

- Horst Simon, NERSC

- my colleges at HLRS

#### **Conclusions**

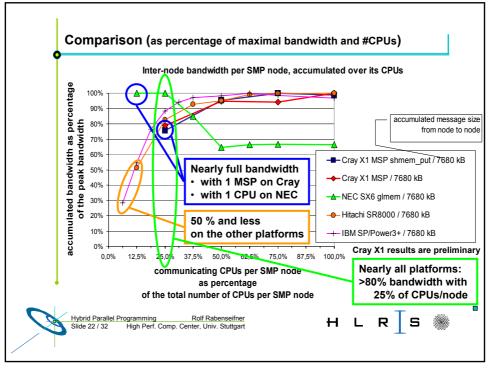

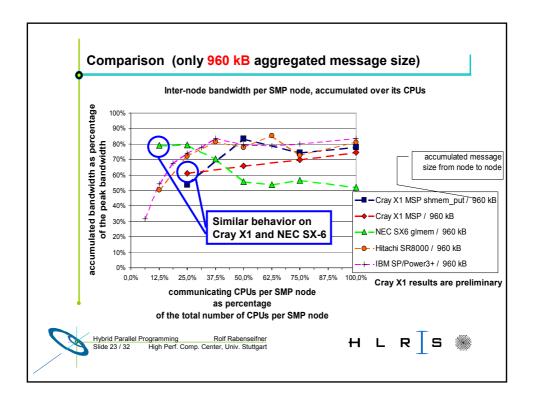

- Cray X1 with MSPs (1 node = 4 MSPs) and NEC SX-5/6:

- well designed hybrid MPI+OpenMP masteronly scheme

- Cray X1 with SSPs (1 node = 16 SSPs)

- hybrid programming: 1 SSP cannot saturate inter-node bandwidth

- Other platforms

- masteronly style cannot saturate inter-node bandwidth

- · Pure MPI and hybrid masteronly:

- idling CPUs (while one is communicating)

- · Optimal performance:

- overlapping of communication & computation

- → extreme programming effort

- optimal throughput

- → reuse of idling CPUs by other applications

- · single threaded, vectorized, low-priority, small-medium memory needs

See also <u>www.hlrs.de/people/rabenseifner</u> → list of publications