## Hybrid MPI & OpenMP Parallel Programming

## MPI + OpenMP and other models on clusters of SMP nodes

Rolf Rabenseifner<sup>1)</sup>

Georg Hager<sup>2)</sup>

Gabriele Jost<sup>3)</sup>

Gabriele.Jost@amd.com

Rabenseifner@hlrs.de

Georg.Hager@rrze.uni-erlangen.de

- 1) High Performance Computing Center (HLRS), University of Stuttgart, Germany

- <sup>2)</sup> Regional Computing Center (RRZE), University of Erlangen, Germany

- 3) AMD, USA, formerly Texas Advanced Computing Center, USA

PRACE Winter School: "Hybrid Programming on Massively Parallel Architectures" Feb. 6–10, 2011, CINECA, Bologna, Italy

ogramming

Höchstleistungsrechenzentrum Stuttgart

### **Outline**

|   | <u>slide nu</u>                                                                    | <u>ımber</u> |                      |

|---|------------------------------------------------------------------------------------|--------------|----------------------|

| • | Introduction / Motivation                                                          | 2            |                      |

| • | Programming models on clusters of SMP nodes                                        | 6            |                      |

| • | Case Studies / pure MPI vs hybrid MPI+OpenMP                                       | 13           | \( \) 14:30 - 16:10  |

| • | Practical "How-To" on hybrid programming                                           | 41           |                      |

| • | Mismatch Problems                                                                  | 81           |                      |

| • | Opportunities: Application categories that can benefit from hybrid parallelization | 110          | ,                    |

| • | Thread-safety quality of MPI libraries                                             | 120          |                      |

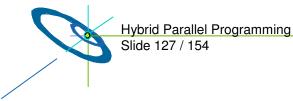

| • | Tools for debugging and profiling MPI+OpenMP                                       | 126          | <b>16:30 – 17:20</b> |

| • | Other options on clusters of SMP nodes                                             | 133          |                      |

| • | Summary                                                                            | 147          |                      |

| • | Appendix                                                                           | 155          |                      |

| • | Content (detailed)                                                                 | 172          |                      |

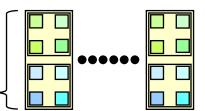

cores

shared

#### **Motivation**

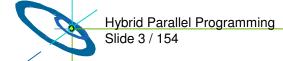

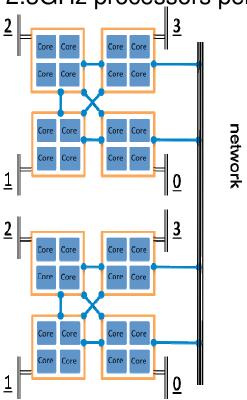

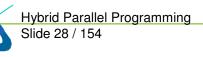

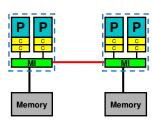

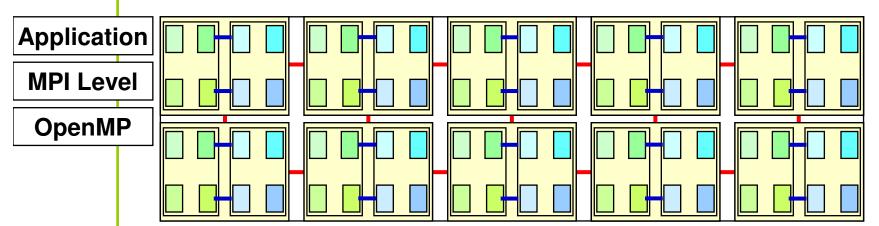

- Efficient programming of clusters of SMP nodes SMP nodes:

- Dual/multi core CPUs

- Multi CPU shared memory

- Multi CPU ccNUMA

- Any mixture with shared memory programming model

- Hardware range

- mini-cluster with dual-core CPUs

- ..

- large constellations with large SMP nodes

- ... with several sockets (CPUs) per SMP node

- ... with several cores per socket

- → Hierarchical system layout

- Hybrid MPI/OpenMP programming seems natural

- MPI between the nodes

- OpenMP inside of each SMP node

ccNUMA node

Cluster of ccNUMA/SMP nodes

SMP nodes

### **Motivation**

- Which programming model is fastest?

- MPI everywhere?

Fully hybrid MPI & OpenMP?

Something between? (Mixed model)

Often hybrid programming slower than pure MPI

- Examples, Reasons, ...

#### Goals of this tutorial

- Sensitize to problems on clusters of SMP nodes

- see sections → Case studies

- → Mismatch problems

- Technical aspects of hybrid programming

- see sections → Programming models on clusters

- → Examples on hybrid programming

- Opportunities with hybrid programming

- see section → Opportunities: Application categories that can benefit from hybrid paralleliz.

- Issues and their Solutions

- with sections → Thread-safety quality of MPI libraries

- → Tools for debugging and profiling for MPI+OpenMP

- Less frustration &

- More **success**

- with your parallel program on clusters of SMP nodes

#### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

- Mismatch Problems

- Opportunities:

Application categories that can benefit from hybrid parallelization

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

Rabenseifner, Hager, Jost

- Other options on clusters of SMP nodes

- Summary

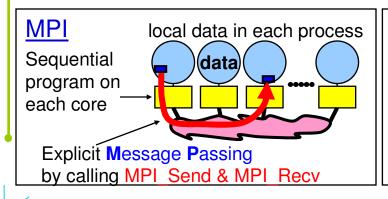

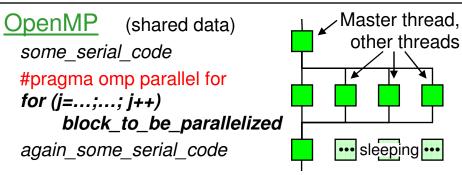

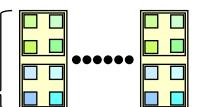

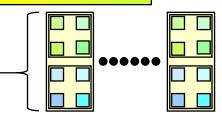

## Major Programming models on hybrid systems

- Pure MPI (one MPI process on each core)

- Hybrid MPI+OpenMP

- shared memory OpenMP

- distributed memory MPI

OpenMP inside of the SMP nodes

MPI between the nodes via node interconnect

Node Interconnect

- Other: Virtual shared memory systems, PGAS, HPF, ...

- Often hybrid programming (MPI+OpenMP) slower than pure MPI

- why?

Hybrid Parallel Programming Slide 7 / 154

Rabenseifner, Hager, Jost

## **Parallel Programming Models on Hybrid Platforms**

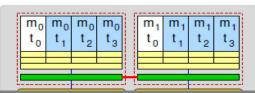

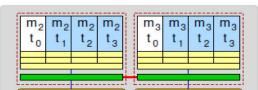

pure MPI one MPI process on each core

hybrid MPI+OpenMP

MPI: inter-node communication OpenMP: inside of each SMP node OpenMP only distributed virtual shared memory

No overlap of Comm. + Comp. MPI only outside of parallel regions of the numerical application code

Overlapping Comm. + Comp. MPI communication by one or a few threads while other threads are computing

Masteronly MPI only outside of parallel regions

#### **Pure MPI**

pure MPI one MPI process on each core

#### Advantages

- No modifications on existing MPI codes

- MPI library need not to support multiple threads

#### Major problems

Rabenseifner, Hager, Jost

- Does MPI library uses internally different protocols?

- Shared memory inside of the SMP nodes

- Network communication between the nodes

- Does application topology fit on hardware topology?

- Unnecessary MPI-communication inside of SMP nodes!

Discussed in detail later on in the section Mismatch Problems

### **Hybrid Masteronly**

Masteronly MPI only outside of parallel regions

#### **Advantages**

- No message passing inside of the SMP nodes

- No topology problem

```

for (iteration ....)

#pragma omp parallel

numerical code

/*end omp parallel */

/* on master thread only */

MPI Send (original data

to halo areas

in other SMP nodes)

MPI_Recv (halo data

from the neighbors)

} /*end for loop

```

#### **Major Problems**

- All other threads are sleeping while master thread communicates!

- Which inter-node bandwidth?

- MPI-lib must support at least MPI THREAD\_FUNNELED

→ Section Thread-safety quality of MPI libraries

#### **Overlapping Communication and Computation**

MPI communication by one or a few threads while other threads are computing

```

if (my_thread_rank < ...) {

MPI_Send/Recv....

i.e., communicate all halo data

} else {

Execute those parts of the application

that do not need halo data

(on non-communicating threads)

}</pre>

```

Execute those parts of the application that <u>need</u> halo data (on <u>all</u> threads)

## Pure OpenMP (on the cluster)

OpenMP only distributed virtual shared memory

- Distributed shared virtual memory system needed

- Must support clusters of SMP nodes

- e.g., Intel® Cluster OpenMP

- Shared memory parallel inside of SMP nodes

- Communication of modified parts of pages at OpenMP flush (part of each OpenMP barrier)

Experience:

→ Mismatch section

i.e., the OpenMP memory and parallelization model is prepared for clusters!

#### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

#### Case Studies / pure MPI vs hybrid MPI+OpenMP

- The Multi-Zone NAS Parallel Benchmarks

- For each application we discuss:

- Benchmark implementations based on different strategies and programming paradigms

- Performance results and analysis on different hardware architectures

- Compilation and Execution Summary

Gabriele Jost (University of Texas, TACC/Naval Postgraduate School, Monterey CA)

- Practical "How-To" on hybrid programming

- Mismatch Problems

- Opportunities: Application categories that can benefit from hybr

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

Rabenseifner, Hager, Jost

- Other options on clusters of SMP nodes

- Summary

Hybrid Parallel Programming

Slide 13 / 154

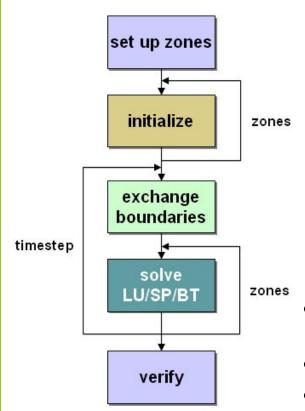

#### The Multi-Zone NAS Parallel Benchmarks

Rabenseifner, Hager, Jost

|                             | MPI/OpenMP            | MLP                 | Nested<br>OpenMP |

|-----------------------------|-----------------------|---------------------|------------------|

| Time step                   | sequential sequential |                     | sequential       |

| inter-zones                 | MPI<br>Processes      | MLP<br>Processes    | OpenMP           |

| exchange boundaries Call MP |                       | data copy+<br>sync. | OpenMP           |

| intra-zones                 | OpenMP                | OpenMP              | OpenMP           |

- Multi-zone versions of the NAS Parallel Benchmarks LU,SP, and BT

- Two hybrid sample implementations

- Load balance heuristics part of sample codes

- www.nas.nasa.gov/Resources/Software/software.html

## MPI/OpenMP BT-MZ

# call omp\_set\_numthreads (weight) do step = 1, itmax call exch\_qbc(u, qbc, nx,...)

#### call mpi\_send/recv

```

do zone = 1, num_zones

if (iam .eq. pzone_id(zone)) then

call zsolve(u,rsd,...)

end if

end do

end do

```

```

subroutine zsolve(u, rsd,...)

!$OMP PARALLEL DEFAUL (SHARED)

!$OMP& PRIVATE(m,i,j,k...)

do k = 2, nz-1

!$OMP DO

do j = 2, ny-1

do i = 2, nx-1

do m = 1, 5

u(m, i, j, k) =

dt*rsd(m,i,j,k-1)

end do

end do

end do

!$OMP END DO nowait

end do

!$OMP END PARALLEL

```

## **Pipelined Thread Execution in SSOR**

```

subroutine ssor

!$OMP PARALLEL DEFAULT (SHARED)

!$OMP& PRIVATE(m, i, j, k...)

call sync1 ()

do k = 2, nz-1

!SOMP DO

do j = 2, ny-1

do i = 2, nx-1

do m = 1, 5

rsd(m, i, j, k) =

dt*rsd(m,i,j,k-1) + ...

end do

end do

end do

!$OMP END DO nowait

end do

call sync2 ()

!$OMP END PARALLEL

```

```

subbroutine sync1

...neigh = iam -1

do while (isync(neigh) .eq. 0)

!$OMP FLUSH(isync)

end do

isync(neigh) = 0

!$OMP FLUSH(isync)

subroutine sync2

neigh = iam -1

do while (isync(neigh) .eq. 1)

!$OMP FLUSH(isync)

end do

isync(neigh) = 1

!$OMP FLUSH(isync)

```

ost III

#### **Benchmark Characteristics**

- Aggregate sizes:

- Class D: 1632 x 1216 x 34 grid points

- Class E: 4224 x 3456 x 92 grid points

- **BT-MZ:** (Block tridiagonal simulated CFD application)

- Alternative Directions Implicit (ADI) method

- #Zones: 1024 (D), 4096 (E)

- Size of the zones varies widely:

- large/small about 20

- requires multi-level parallelism to achieve a good load-balance

- **LU-MZ:** (LU decomposition simulated CFD application)

- SSOR method (2D pipelined method)

- #Zones: 16 (all Classes)

- Size of the zones identical:

- no load-balancing required

- limited parallelism on outer level

- **SP-MZ:** (Scalar Pentadiagonal simulated CFD application)

- #Zones: 1024 (D), 4096 (E)

- Size of zones identical

- no load-balancing required

Hybrid Parallel Programming

Slide 17 / 154

Rabenseifner, Hager, Jost

Pure MPI: Loadbalancing problems!

Good candidate for MPI+OpenMP

> Limitted MPI Parallelism:

→ MPI+OpenMP increases Parallelism

Load-balanced on MPI level: Pure MPI should perform best

### **Benchmark Architectures**

- Sun Constellation (Ranger)

- Cray XT5 (-skipped-)

- IBM Power 6

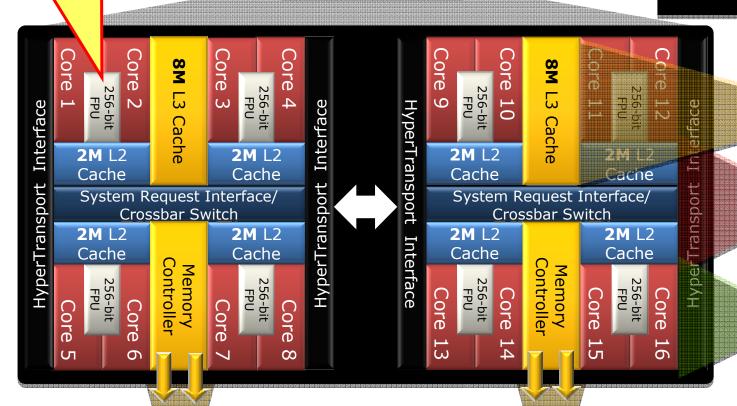

## **Sun Constellation Cluster Ranger (1)**

Located at the Texas Advanced Computing Center (TACC), University of Texas at Austin (http://www.tacc.utexas.edu)

3936 Sun Blades, 4 AMD Quad-core 64bit 2.3GHz processors per

node (blade), 62976 cores total

123TB aggregrate memory

Peak Performance 579 Tflops

- InfiniBand Switch interconnect

- Sun Blade x6420 Compute Node:

- 4 Sockets per node

- 4 cores per socket

- HyperTransport System Bus

- 32GB memory

## Sun Constellation Cluster Ranger (2)

- Compilation:

- PGI pgf90 7.1

- i.e., with OpenMP

- mpif90 -tp barcelona-64 -r8 -mp

- Cache optimized benchmarks Execution:

- MPI MVAPICH

- setenv OMP NUM THREADS nthreads

- Ibrun numactl bt-mz.exe

- numactl controls

- Socket affinity: select sockets to run

- Core affinity: select cores within socket

- Memory policy:where to allocate memory

Rabenseifner, Hager, Jost

http://www.halobates.de/numaapi3.pdf

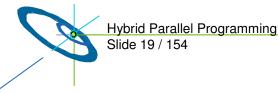

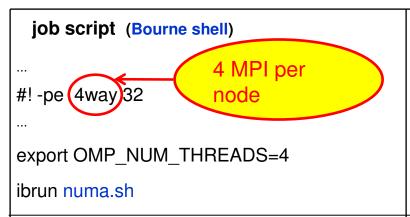

## SUN: Running hybrid on Sun Constellation **Cluster Ranger**

- Highly hierarchical

- **Shared Memory:**

- Cache-coherent, Nonuniform memory access (ccNUMA) 16-way Node (Blade)

- Distributed memory:

- Network of ccNUMA blades

- Core-to-Core

- Socket-to-Socket

- Blade-to-Blade

- **Chassis-to-Chassis**

network

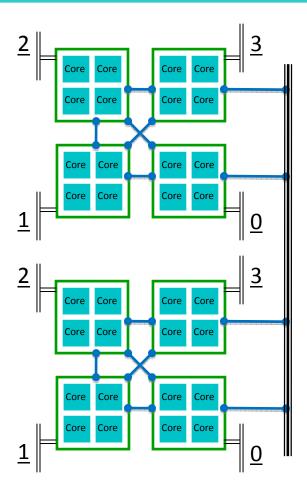

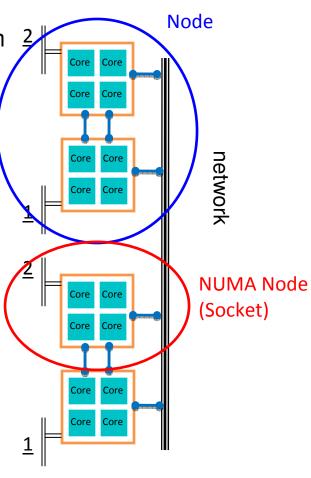

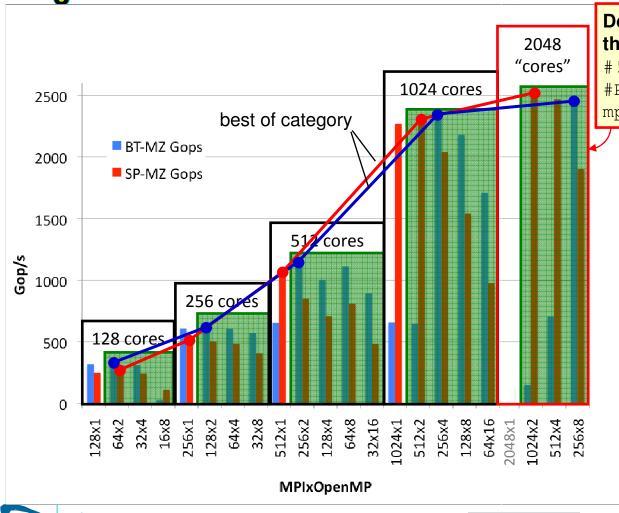

## SUN: NPB-MZ Class E Scalability on Ranger

#### BT

Significant improvement (235%):

Load-balancing issues solved with MPI+OpenMP

#### SP

Pure MPI is already load-balanced.

But hybrid 9.6% faster, due to smaller message rate at NIC

Cannot be build for 8192 processes!

#### Hybrid:

SP: still scales

BT: does not scale

Scalability in Mflops

MPI/OpenMP outperforms pure MPI

Use of numactl essential to achieve scalability

Hybrid Parallel Programming

Slide 22 / 154

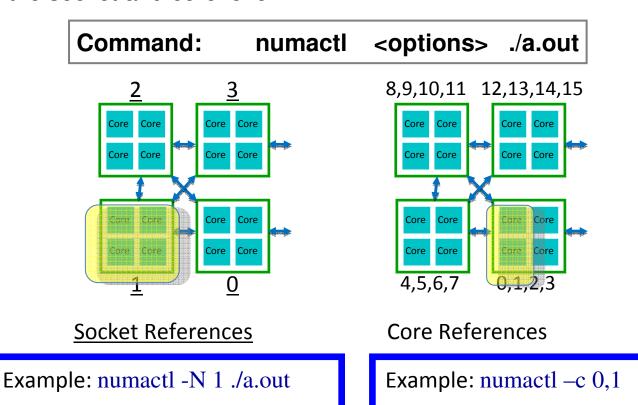

#### **NUMA Control: Process Placement**

Affinity and Policy can be changed externally through numactl at the socket and core level.

Hybrid Parallel Programming Slide 23 / 154

Rabenseifner, Hager, Jost

## **NUMA Operations: Memory Placement**

Memory: Socket References

#### Memory allocation:

- MPI

- local allocation is best

- OpenMP

- Interleave best for large, completely shared arrays that are randomly accessed by different threads

- local best for private arrays

- Once allocated, a memory-structure is fixed

Example: numactl -N 1 -1 ./a.out

## **NUMA Operations** (cont. 3)

|                 | cmd     | option     | arguments                                           | description                                                       |

|-----------------|---------|------------|-----------------------------------------------------|-------------------------------------------------------------------|

| Socket Affinity | numacti | -N         | {0,1,2,3}                                           | Only execute process on cores of this (these) socket(s).          |

| Memory Policy   | numactl | -1         | {no argument}                                       | Allocate on current socket.                                       |

| Memory Policy   | numactl | -i         | {0,1,2,3}                                           | Allocate round robin (interleave) on these sockets.               |

| Memory Policy   | numactl | preferred= | {0,1,2,3}<br>select only one                        | Allocate on this<br>socket; fallback<br>to any other if<br>full . |

| Memory Policy   | numacti | -m         | {0,1,2,3}                                           | Only allocate on this (these) socket(s).                          |

| Core Affinity   | numacti | -C         | {0,1,2,3,<br>4,5,6,7,<br>8,9,10,11,<br>12,13,14,15} | Only execute process on this (these) Core(s).                     |

Hybrid Parallel Programming Slide 25 / 154

Rabenseifner, Hager, Jost

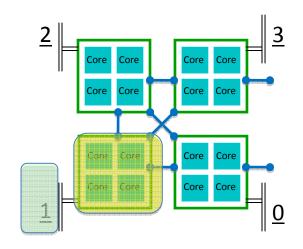

### Hybrid Batch Script: 4 tasks, 4 threads/task

#### job script (C shell)

#!-pe 4way 32

setenv OMP\_NUM\_THREADS 4

ibrun numa.csh

#### numa.sh

#!/bin/bash

export MV2\_USE\_AFFINITY=0

export MV2\_ENABLE\_AFFINITY=0

export VIADEV\_USE\_AFFINITY=0

#TasksPerNode

TPN=`echo \$PE | sed 's/way//'`

[!\$TPN] && echo TPN NOT defined!

[!\$TPN] && exit 1

socket=\$((\$PMI\_RANK % \$TPN))

https://doi.org/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/10.1001/

#### numa.csh

#!/bin/tcsh

setenv MV2\_USE\_AFFINITY 0

setenv MV2\_ENABLE\_AFFINITY 0

setenv VIADEV\_USE\_AFFINITY 0

#TasksPerNode

set TPN = `echo \$PE | sed 's/way//'

if(! \${%TPN}) echo TPN NOT defined!

if(! \${%TPN}) exit 0

@ socket = \$PMI\_RANK % \$TPN

$\omega$  Socket =  $\varphi$ FIVII\_HAINK %  $\varphi$ 1FIV

numactl -N \$socket -m \$socket ./a.out

H

for mvapich2

## bt-mz.1024x8 yields best load-balance

```

-pe 2way 8192

export OMP_NUM_THREADS=8

my_rank=$PMI_RANK

local_rank=$(( $my_rank % $myway ))

numnode=$(( $local_rank + 1 ))

```

#### Original:

numactl -N \$numnode -m \$numnode \$\*

#### **Bad performance!**

- Each process runs 8 threads on 4 cores

- Memory allocated on one socket

## network

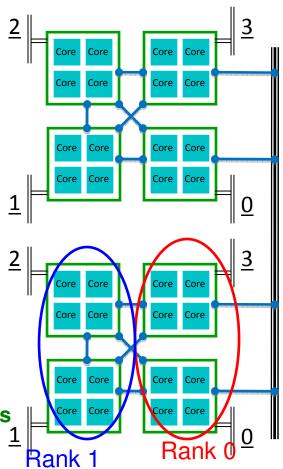

## Numactl - Pitfalls: Using Threads across Sockets

#### bt-mz.1024x8

```

export OMP_NUM_THREADS=8

my_rank=$PMI_RANK

local_rank=$(( $my_rank % $myway ))

numnode=$(( $local_rank + 1 ))

```

#### Original:

numactl -N \$numnode -m \$numnode \$\*

#### Modified:

```

if [ $local_rank -eq 0 ]; then

numactl -N 0,3 -m 0,3 $*

else

numactl -N 1,2 -m 1,2 $*

fi

```

#### **Achieves Scalability!**

Process uses cores and memory across 2 sockets

Rabenseifner, Hager, Jost

Suitable for 8 threads

## **Cray XT5**

Results obtained by the courtesy of the HPCMO Program and the Engineer Research and Development Center Major Shared Resource Center, Vicksburg, MS (http://www.erdc.hpc.mil/index)

- Cray XT5 is located at the Arctic Region Supercomputing Center (ARSC) (http://www.arsc.edu/resources/pingo)

- 432- Cray XT5 compute nodes with

- 32 GB of shared memory per node (4 GB per core)

- 2 quad core 2.3 GHz AMD Opteron processors per node.

- 1 Seastar2+ Interconnect Module per node.

- Cray Seastar2+ Interconnect between all compute and login nodes

## **Cray XT5: NPB-MZ Class D Scalability**

Rabenseifner, Hager, Jost

Hybrid Parallel Programming

Slide 30 / 154

Results reported for Class D on 256-2048 cores

> Expected: **#MPI** processes limited

- SP-MZ pure MPI scales up to 1024 cores

- SP-MZ MPI/OpenMP scales to 2048 cores

- SP-MZ MPI/OpenMP outperforms pure MPI for 1024 cores **Unexpected!**

- BT-MZ MPI does not scale

- BT-MZ MPI/OpenMP scales to 2048 cores, outperforms pure MP

Expected: Load-Imbalance for pure MPI

## **Cray XT5: CrayPat Performance Analysis**

- module load xt-craypat

- Compilation:

- → ftn -fastsse -tp barcelona-64 -r8 -mp=nonuma,[trace]

- Instrument:

- > pat\_build -w -T TraceOmp, -g mpi,omp bt.exe bt.exe.pat

- Execution :

- ➤ (export PAT\_RT\_HWPC {0,1,2,...})

- > export OMP\_NUM\_THREADS 4

- > aprun -n NPROCS -S 1 -d 4 ./bt.exe.pat

- Generate report:

- pat\_report -O

load\_balance,thread\_times,program\_time,mpi\_callers -O

profile\_pe.th \$1

## **Cray XT5: BT-MZ 32x4 Function Profile**

```

F42

!$OMP PARALLEL DEFAULT(SHARED) PRIVATE(n,m,k,i,j,ksize)

F43

L$OMP& SHARED(dz5,dz4,dz3,dz2,dz1,tz2,tz1,dt,c1345,c4,c3,con43,c3c4,c1,

r45

c2.nx.ny.nz)

1$UNES

+46

+47

ead='HIDE'

Compute the indices for storing the block-diagonal matrix;

F50

determine c (labeled f) and s jacobians

!$OMP DO

+52

+53

+54

+55

+56

+57

+58

+60

+61

+62

+63

+64

do j = 1, ny-2

do i = 1, nx-2

e .LOOP@li.43

do k = 0, ksize

B_.LOOP@li.43

e_.LOOP@li.46

tmp1 = 1.d0 / u(1,i,j,k)

e_rhs_.MASTER@li.291

tmp2 = tmp1 * tmp1

e_rhs_.LOOP@li.187

tmp3 = tmp1 * tmp2

e rhs .LOOP@li.53

e rhs .LOOP@li.76

f_{iac}(1,1,k) = 0.d0

f_{i,j,ac}(1,2,k) = 0.d0

e_rhs_.LOOP@li.28

f_{iac}(1.3.k) = 0.d0

e_rhs_.LOOP@li.297

f_{jac}(1,4,k) = 1.d0

lize_.LOOP@li.40

-65

f.iac(1,5,k) = 0.d0

e_rhs_.L00P@li.381

168 |add .LOOP@li.22

1,2% | 0,016/53 | 0,0059/2 |

19.5% |

Hybrid

2.1% | 0.030491 |

1040 IMPI

Slide

1.8% | 0.026193 | 0.111613 | 81.6% | 105 | mpi_waitall_

```

## Cray XT5: BT-MZ Load-Balance 32x4 vs 128x1

| Table 2: Load Balance across PE's by FunctionGroup                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time %   Time   Calls  Experiment=1<br>                                                                                                                          |

| 100,0%   1,782603   18662   Total                                                                                                                                |

| 86.1%   1.535163   7783   USER                                                                                                                                   |

| 2.7%   1.535987   6813  pe.0                                                                                                                                     |

| 3   0.7%   1.535987   6188   thread.1<br>3   0.7%   1.535871   6188   thread.3<br>3   0.7%   1.535829   6188   thread.2<br>3   0.7%   1.466954   6813   thread.0 |

| 2.7%   1.535147   7783  pe.18                                                                                                                                    |

| 3   0.7%   1.535147   7072   thread.1<br>3   0.7%   1.534995   7072   thread.3<br>3   0.7%   1.534968   7072   thread.2<br>3   0.6%   1.290502   7783   thread.0 |

| 2,7%   1,534239   7783  pe,16                                                                                                                                    |

| 3   0.7%   1.534239   7072   thread.1<br>3   0.7%   1.534101   7072   thread.3<br>3   0.7%   1.534076   7072   thread.2<br>3   0.6%   1.268085   7783   thread.0 |

bt-mz-C.128x1

- maximum, median, minimum PE are shown

- bt-mz.C.128x1 shows large imbalance in User and MPI time

- bt-mz.C.32x4 shows well balanced times

bt-mz-C.32x4

Hybrid Parallel Programming Slide 33 / 154

Rabenseifner, Hager, Jost

#### **IBM Power 6**

- Results obtained by the courtesy of the HPCMO Program and the Engineer Research and Development Center Major Shared Resource Center, Vicksburg, MS (<a href="http://www.erdc.hpc.mil/index">http://www.erdc.hpc.mil/index</a>)

- The IBM Power 6 System is located at (http://www.navo.hpc.mil/davinci\_about.html)

- 150 Compute Nodes

- 32 4.7GHz Power6 Cores per Node (4800 cores total)

- 64 GBytes of dedicated memory per node

- QLOGOC Infiniband DDR interconnect

- IBM MPI: MPI 1.2 + MPI-IO

- mpxlf\_r -Q4 -qarch=pwr6 -qtune=pwr6 -qsmp=omp

Flag was essential to achieve full compiler optimization in presence of OMP directives!

- **Execution:**

- poe launch \$PBS\_O\_WORKDIR./sp.C.16x4.exe

## SC 10 New Orleans, L

## NPB-MZ Class D on IBM Power 6: Exploiting SMT for 2048 Core Results

## Doubling the number of threads through hyperthreading (SMT):

#!/bin/csh

#PBS -1 select=32:ncpus=64:

mpiprocs=NP:ompthreads=NT

- Results for 128-2048 cores

- Only 1024 cores were available for the experiments

- BT-MZ and SP-MZ show benefit from Simultaneous Multithreading (SMT): 2048 threads on 1024 cores

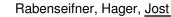

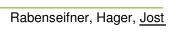

## **Conventional Multi-Threading**

- Threads alternate

- Nothing shared

Charles Grassl, IBM

# **Simultaneous Multi-Threading**

- Simultaneous execution

- Shared registers

- Shared functional units

FFZE

Charles Grassl, IBM

Hybrid Parallel Programming Slide 37 / 154

Rabenseifner, Hager, Jost

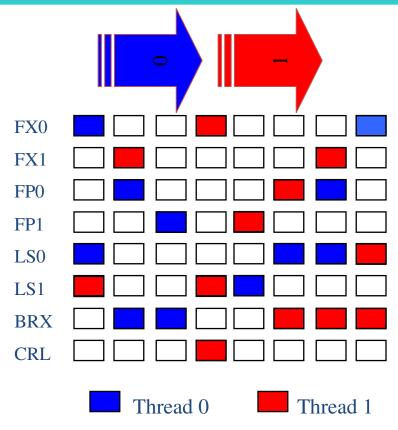

# AMD OPTERON™ 6200 SERIES PROCESSOR ("INTERLAGOS")

FPUs are shared between two cores

Multi- Chip Module (MCM) Package

Same platform as AMD Opteron™ 6100 Series processor.

16M L3 cache

(Up to 32M) L2+L3 cache)

8, 12, 8 16 core models

Note: Graphic may not be fully representative of actual layout

4 DDR3 memory channels supporting LRDIMM, ULV-DIMM, UDIMM, & RDIMM

From: AMD "Bulldozer" Technology, © 2011 AMD

# **Performance Analysis on IBM Power 6**

- Compilation:

- mpxlf\_r -O4 -qarch=pwr6 -qtune=pwr6 -qsmp=omp -pg

- Execution :

- export OMP\_NUM\_THREADS 4

- poe launch \$PBS\_O\_WORKDIR./sp.C.16x4.exe

- Generates a file gmount.MPI\_RANK.out for each MPI Process

- Generate report:

- gprof sp.C.16x4.exe gmon\*

| % cumulative |     | self    |         | self   | total   |         |                               |

|--------------|-----|---------|---------|--------|---------|---------|-------------------------------|

| tim          | ne  | seconds | seconds | calls  | ms/call | ms/call | name                          |

| 16.          | . 7 | 117.94  | 117.94  | 205245 | 0.57    | 0.57    | .0100x_solve0OL01 [2]         |

| 14.          | 6   | 221.14  | 103.20  | 205064 | 0.50    | 0.50    | .0150z_solve0OL01 [3]         |

| 12.          | . 1 | 307.14  | 86.00   | 205200 | 0.42    | 0.42    | .0120y_solve0OL01 [4]         |

| 6.           | 2   | 350.83  | 43.69   | 205300 | 0.21    | 0.21    | .080compute_rhs00L0100L06 [5] |

## **Conclusions:**

#### BT-MZ:

- Inherent workload imbalance on MPI level

- #nprocs = #nzones yields poor performance

- #nprocs < #zones => better workload balance, but decreases parallelism

- Hybrid MPI/OpenMP yields better load-balance, maintains amount of parallelism

#### SP-MZ:

- > No workload imbalance on MPI level, pure MPI should perform best

- MPI/OpenMP outperforms MPI on some platforms due contention to network access within a node

#### LU-MZ:

- ➤ Hybrid MPI/OpenMP increases level of parallelism

- "Best of category" depends on many factors

- Depends on many factors

- > Hard to predict

- Good thread affinity is essential

## **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

**Georg Hager,** Regionales Rechenzentrum Erlangen (RRZE)

- Mismatch Problems

- Application categories that can benefit from hybrid parallelizati

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

- Other options on clusters of SMP nodes

- Summary

# **Hybrid Programming How-To: Overview**

- A practical introduction to hybrid programming

- How to compile and link

- Getting a hybrid program to run on a cluster

- Running hybrid programs efficiently on multi-core clusters

- Affinity issues

- ccNUMA

- Bandwidth bottlenecks

- Intra-node MPI/OpenMP anisotropy

- MPI communication characteristics

Rabenseifner, Hager, Jost

- OpenMP loop startup overhead

- Thread/process binding

## How to compile, link and run

- Use appropriate OpenMP compiler switch (-openmp, -xopenmp, -mp, -qsmp=openmp, ...) and MPI compiler script (if available)

- Link with MPI library

- Usually wrapped in MPI compiler script

- If required, specify to link against thread-safe MPI library

- Often automatic when OpenMP or auto-parallelization is switched on

- Running the code

- Highly non-portable! Consult system docs! (if available...)

- If you are on your own, consider the following points

- Make sure OMP\_NUM\_THREADS etc. is available on all MPI processes

- Start "env VAR=VALUE ... < YOUR BINARY>" instead of your binary alone

- Use Pete Wyckoff's mpiexec MPI launcher (see below): http://www.osc.edu/~pw/mpiexec

Rabenseifner, Hager, Jost

Figure out how to start less MPI processes than cores on your nodes

# Some examples for compilation and execution (1)

#### NEC SX9

- NEC SX9 compiler

- mpif90 -C hopt -P openmp ... # -ftrace for profiling info

- Execution:

- \$ export OMP\_NUM\_THREADS=<num\_threads>

- \$ MPIEXPORT="OMP\_NUM\_THREADS"

- \$ mpirun -nn <# MPI procs per node> -nnp <# of nodes> a.out

### Standard Intel Xeon cluster (e.g. @HLRS):

- Intel Compiler

- mpif90 -openmp ...

- Execution (handling of OMP NUM THREADS, see next slide):

\$ mpirun\_ssh -np <num MPI procs> -hostfile machines a.out

## Some examples for compilation and execution (2)

### Handling of OMP\_NUM\_THREADS

- without any support by mpirun:

- E.g. with mpich-1

- Problem: mpirun has no features to export environment variables to the via ssh automatically started MPI processes

- Solution: Set export OMP\_NUM\_THREADS=<# threads per MPI process> in ~/.bashrc (if a bash is used as login shell)

- If you want to set OMP NUM THREADS individually when starting the MPI processes:

- Add test -s ~/myexports && . ~/myexports in your ~/.bashrc

- Add echo '\$OMP\_NUM\_THREADS=<# threads per MPI process>' > ~/myexports before invoking mpirun

- Caution: Several invocations of mpirun cannot be executed at the same time with this trick!

Slide 45 / 154

# Some examples for compilation and execution (3)

Handling of OMP\_NUM\_THREADS (continued)

• with support by OpenMPI -x option:

```

export OMP_NUM_THREADS= <# threads per MPI process>

mpiexec -x OMP_NUM_THREADS -n <# MPI processes> ./executable

```

# Some examples for compilation and execution (4)

### Sun Constellation Cluster:

- mpif90 -fastsse -tp barcelona-64 -mp ...

- SGE Batch System

- setenv OMP\_NUM\_THREADS

- ibrun numactl.sh a.out

- Details see TACC Ranger User Guide (www.tacc.utexas.edu/services/userguides/ranger/#numactl)

### Cray XT5:

- ftn -fastsse -tp barcelona-64 -mp=nonuma ...

- aprun -n nprocs -N nprocs\_per\_node a.out

# Interlude: Advantages of mpiexec or similar mechanisms

- Uses PBS/Torque Task Manager ("TM") interface to spawn MPI processes on nodes

- As opposed to starting remote processes with ssh/rsh:

- Correct CPU time accounting in batch system

- Faster startup

- Safe process termination

- Understands PBS per-job nodefile

- Allowing password-less user login not required between nodes

- Support for many different types of MPI

- All MPICHs, MVAPICHs, Intel MPI, ...

- Interfaces directly with batch system to determine number of procs

- Downside: If you don't use PBS or Torque, you're out of luck...

- Provisions for starting less processes per node than available cores

- Required for hybrid programming

Rabenseifner, Hager, Jost

"-pernode" and "-npernode #" options – does not require messing around with nodefiles

## Running the code

## Examples with mpiexec

- Example for using mpiexec on a dual-socket quad-core cluster:

- \$ export OMP\_NUM\_THREADS=8

- \$ mpiexec -pernode ./a.out

- Same but 2 MPI processes per node:

- \$ export OMP\_NUM\_THREADS=4

- \$ mpiexec -npernode 2 ./a.out

- Pure MPI:

- \$ export OMP\_NUM\_THREADS=1 # or nothing if serial code

- \$ mpiexec ./a.out

## Running the code efficiently?

- Symmetric, UMA-type compute nodes have become rare animals

- NFC SX

- Intel 1-socket ("Port Townsend/Melstone/Lynnfield") see case studies

- Hitachi SR8000, IBM SP2, single-core multi-socket Intel Xeon... (all dead)

- Instead, systems have become "non-isotropic" on the node level

- ccNUMA (AMD Opteron, SGI Altix, IBM Power6 (p575), Intel Nehalem)

- Multi-core, multi-socket

- Shared vs. separate caches

- Multi-chip vs. single-chip

- Separate/shared buses

# Issues for running code efficiently on "non-isotropic" nodes

- ccNUMA locality effects

- Penalties for inter-LD access

- Impact of contention

- Consequences of file I/O for page placement

- Placement of MPI buffers

- Multi-core / multi-socket anisotropy effects

- Bandwidth bottlenecks, shared caches

- Intra-node MPI performance

- Core ↔ core vs. socket ↔ socket

- OpenMP loop overhead depends on mutual position of threads in team

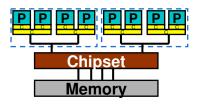

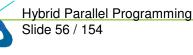

## A short introduction to ccNUMA

- ccNUMA:

- whole memory is transparently accessible by all processors

- but physically distributed

- with varying bandwidth and latency

- and potential contention (shared memory paths)

## Example: HP DL585 G5

## 4-socket ccNUMA Opteron 8220 Server

- **CPU**

- 64 kB L1 per core

- 1 MB L2 per core

- No shared caches

- On-chip memory controller (MI)

- 10.6 GB/s local memory bandwidth

- HyperTransport 1000 network

- 4 GB/s per link per direction

- 3 distance categories for core-to-memory connections:

- same LD

- 1 hop

- 2 hops

- Q1: What are the real penalties for non-local accesses?

- Q2: What is the impact of contention?

Memory

Memory

HT

HT

**Memory**

Memory

Slide 53 / 154

Rabenseifner, Hager, Jost

# SC10 SC11 New Orleans, LA

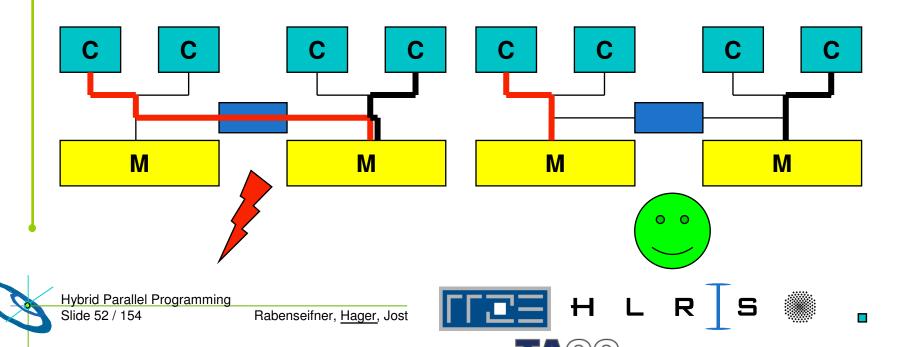

## Effect of non-local access on HP DL585 G5:

**Serial vector triad A(:)**=**B(:)**+**C(:)**\***D(:)**

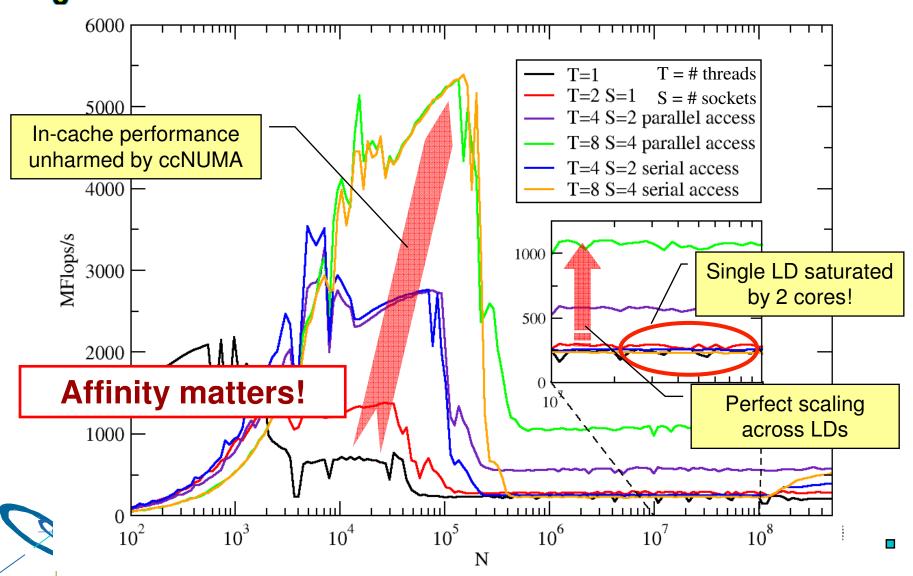

# Contention vs. parallel access on HP DL585 G5

**OpenMP vector triad A(:)=B(:)+C(:)\*D(:)**

## **ccNUMA Memory Locality Problems**

- Locality of reference is key to scalable performance on ccNUMA

- Less of a problem with pure MPI, but see below

- What factors can destroy locality?

- MPI programming:

- processes lose their association with the CPU the mapping took place on originally

- OS kernel tries to maintain strong affinity, but sometimes fails

- Shared Memory Programming (OpenMP, hybrid):

- threads losing association with the CPU the mapping took place on originally

- improper initialization of distributed data

- Lots of extra threads are running on a node, especially for hybrid

- All cases:

- Other agents (e.g., OS kernel) may fill memory with data that prevents optimal placement of user data

# **Avoiding locality problems**

- How can we make sure that memory ends up where it is close to the CPU that uses it?

- See the following slides

- How can we make sure that it stays that way throughout program execution?

- See end of section

# **Solving Memory Locality Problems: First Touch**

"Golden Rule" of ccNUMA:

# A memory page gets mapped into the local memory of the processor that first touches it!

- Except if there is not enough local memory available

- this might be a problem, see later

- Some OSs allow to influence placement in more direct ways

- cf. libnuma (Linux), MPO (Solaris), ...

- Caveat: "touch" means "write", not "allocate"

- Example:

```

double *huge = (double*)malloc(N*sizeof(double));

// memory not mapped yet

for(i=0; i<N; i++) // or i+=PAGE_SIZE

huge[i] = 0.0; // mapping takes place here!</pre>

```

It is sufficient to touch a single item to map the entire page

## ccNUMA problems beyond first touch

- OS uses part of main memory for disk buffer (FS) cache

- If FS cache fills part of memory, apps will probably allocate from foreign domains

- − → non-local access!

- Locality problem even on hybrid and pure MPI with "asymmetric" file I/O, i.e. if not all MPI processes perform I/O

- Remedies

- Drop FS cache pages after user job has run (admin's job)

- · Only prevents cross-job buffer cache "heritage"

- "Sweeper" code (run by user)

- Flush buffer cache after I/O if necessary ("sync" is not sufficient!)

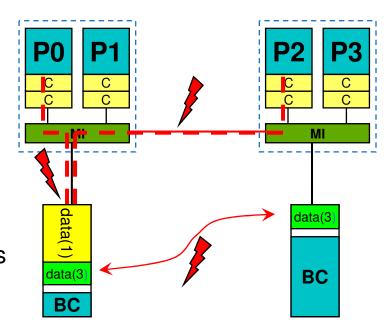

# ccNUMA problems beyond first touch

- Real-world example: ccNUMA vs. UMA and the Linux buffer cache

- Compare two 4-way systems: AMD Opteron ccNUMA vs. Intel UMA, 4 GB main memory

- Run 4 concurrent triads (512 MB each) after writing a large file

- Report performance vs. file size

- Drop FS cache after each data point

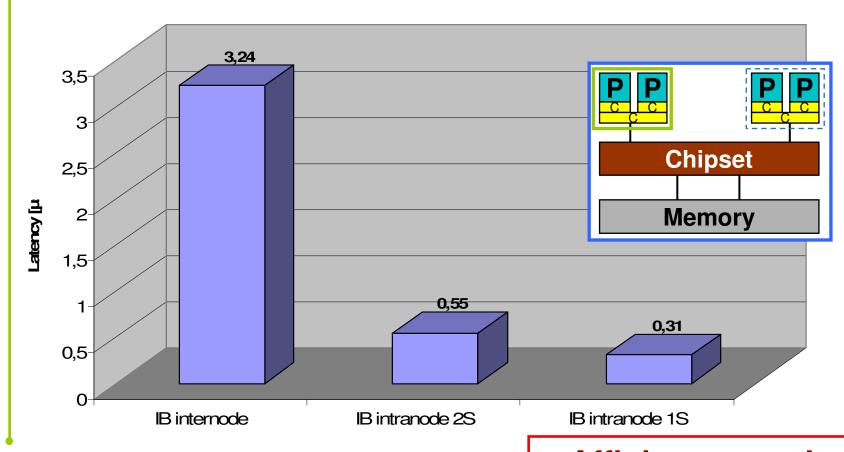

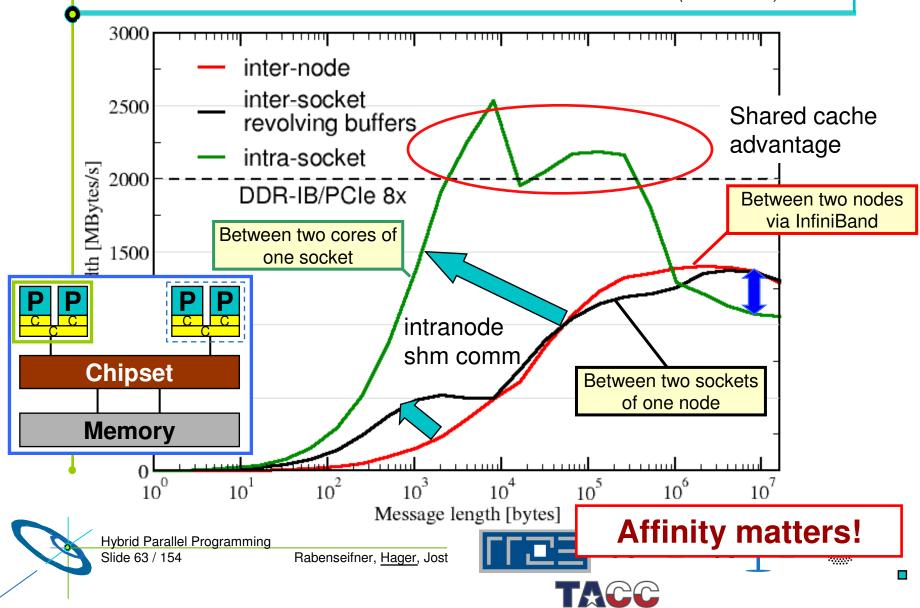

## Intra-node MPI characteristics: IMB Ping-Pong benchmark

Code (to be run on 2 processors): wc = MPI WTIME() do i=1, NREPEAT if(rank.eq.0) then MPI\_SEND (buffer, N, MPI\_BYTE, 1, 0, MPI\_COMM\_WORLD, ierr) MPI RECV (buffer, N, MPI BYTE, 1, 0, MPI COMM WORLD, & status,ierr) else MPI\_RECV(...) MPI SEND (...) Chipset endif enddo **Memory**  $wc = MPI_WTIME() - wc$ Intranode (1S): mpirun -np 2 -pin "1 3" ./a.out Intranode (2S): mpirun -np 2 -pin "2 3" ./a.out Internode: mpirun -np 2 -pernode ./a.out

## **IMB Ping-Pong: Latency**

Intra-node vs. Inter-node on Woodcrest DDR-IB cluster (Intel MPI 3.1)

Rabenseifner, Hager, Jost

## **IMB Ping-Pong: Bandwidth Characteristics**

Intra-node vs. Inter-node on Woodcrest DDR-IB cluster (Intel MPI 3.1)

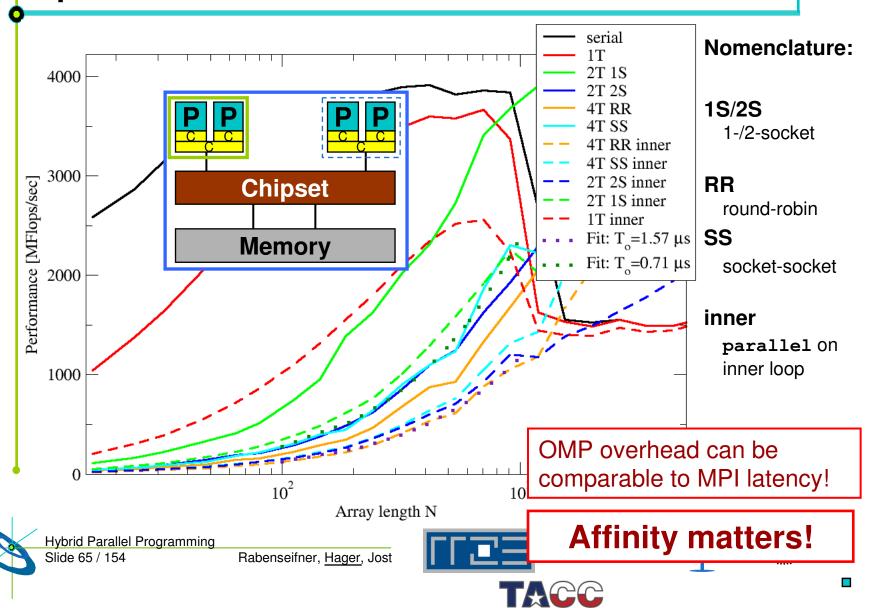

## **OpenMP Overhead**

- As with intra-node MPI, OpenMP loop start overhead varies with the mutual position of threads in a team

- Possible variations

- Intra-socket vs. inter-socket

- Different overhead for "parallel for" vs. plain "for"

- If one multi-threaded MPI process spans multiple sockets,

- ... are neighboring threads on neighboring cores?

- ... or are threads distributed "round-robin" across cores?

- Test benchmark: Vector triad

```

#pragma omp parallel

for (int j=0; j < NITER; j++) {

#pragma omp (parallel) for

for(i=0; i < N; ++i)

a[i]=b[i]+c[i]*d[i];

if (OBSCURE)

dummy (a,b,c,d);

```

Look at performance for small array sizes!

## **OpenMP Overhead**

## Most of the OpenMP overhead is barrier sync!

But how much is it exactly, and does it depend on the topology?

| Overhead            | lin     | CVC              | les: |

|---------------------|---------|------------------|------|

| <b>0 1</b> 01110 au | • • • • | $\mathbf{c}_{j}$ | .00  |

| P | P | P | P |

|---|---|---|---|

|   |   |   | Г |

| 4 Threads               | Q9550 | i7 920 (shared L3) |  |

|-------------------------|-------|--------------------|--|

| (pthreads_barrier_wait) | 42533 | 9820               |  |

| omp barrier (icc 11.0)  | 977   | 814                |  |

| gcc 4.4.3               | 41154 | 8075               |  |

pthreads/gcc → OS kernel call

OpenMP & Intel compiler

| Nehalem 2 Threads       | Shared SMT threads | shared L3 | different socket | <br>  <br>  <br>  <br>  <br> |

|-------------------------|--------------------|-----------|------------------|------------------------------|

| (pthreads_barrier_wait) | 23352              | 4796      | 49237            | -                            |

| omp barrier (icc 11.0)  | 2761               | 479       | 1206             | i i                          |

|                         | •                  |           |                  | Jel.                         |

- SMT can be a performance problem for synchronizing threads

- Topology has an influence on overhead!

Hybrid Parallel Programming Slide 66 / 154

Rabenseifner, Hager, Jost

## Thread/Process Affinity ("Pinning")

- Highly OS-dependent system calls

- But available on all systems

Linux: sched\_setaffinity(), PLPA (see below) -> hwloc

Solaris: processor\_bind()

Windows: SetThreadAffinityMask()

- Support for "semi-automatic" pinning in some compilers/environments

- Intel compilers > V9.1 (KMP\_AFFINITY environment variable)

- Pathscale

- SGI Altix dplace (works with logical CPU numbers!)

- Generic Linux: taskset, numactl, likwid-pin (see below)

- Affinity awareness in MPI libraries

Seen on SUN Ranger slides

- SGI MPT

- OpenMPI

- Intel MPI

Widely usable example: Using PLPA

under Linux!

## **Explicit Process/Thread Binding With PLPA on Linux:**

http://www.open-mpi.org/software/plpa/

- Portable Linux Processor Affinity

- Wrapper library for sched\_\*affinity() functions

- Robust against changes in kernel API

- Example for pure OpenMP: Pinning of threads

```

core numbering!

0...N-1 is not always

#include <plpa.h>

contiguous! If

Pinning

#pragma omp parallel

required, reorder by

available?

a map:

#pragma omp critical

cpu = map[cpu];

if(PLPA_NAME(api_probe)()!=PLPA_PROBE_OK) {

cerr << "PLPA failed!" << endl; exit(1);</pre>

Which CPU

plpa cpu set t msk;

to run on?

PLPA_CPU_ZERO(&msk);

int cpu = omp_get_thread_num();

PLPA_CPU_SET(cpu, &msk);

PLPA_NAME(sched_setaffinity)((pid_t)0, sizeof(cpu_set_t), &msk);

Pin "me"

```

Care about correct

Rabenseifner, Hager, Jost

Memory

## **Process/Thread Binding With PLPA**

- Example for pure MPI: Process pinning

- Bind MPI processes to cores in a cluster of 2x2-core machines

Rabenseifner, Hager, Jost

Hybrid case:

# How do we figure out the topology?

- ... and how do we enforce the mapping without changing the code?

- Compilers and MPI libs may still give you ways to do that

- But LIKWID supports all sorts of combinations:

Like I Knew What

I'm Doing

Open source tool collection (developed at RRZE):

http://code.google.com/p/likwid

## **Likwid Tool Suite**

- Command line tools for Linux:

- works with standard linux 2.6 kernel

- supports Intel and AMD CPUs

- Supports all compilers whose OpenMP implementation is based on pthreads

- Current tools:

- likwid-topology: Print thread and cache topology (similar to Istopo from the hwloc package)

- likwid-pin: Pin threaded application without touching code

- likwid-perfctr: Measure performance counters

- likwid-perfscope: Performance oscilloscope w/ real-time display

- likwid-powermeter: Current power consumption of chip (alpha stage)

- likwid-features: View and enable/disable hardware prefetchers

- likwid-bench: Low-level bandwidth benchmark generator tool

- likwid-mpirun: mpirun wrapper script for easy LIKWID integration

# likwid-topology – Topology information

- Based on cpuid information

- Functionality:

- Measured clock frequency

- Thread topology

- Cache topology

- Cache parameters (-c command line switch)

- ASCII art output (-g command line switch)

- Currently supported:

- Intel Core 2 (45nm + 65 nm)

- Intel Nehalem

- AMD K10 (Quadcore and Hexacore)

- AMD K8

# **Output of likwid-topology**

CPU name: Intel Core i7 processor

CPU clock: 2666683826 Hz

Hardware Thread Topology

Sockets: Cores per socket: Threads per core:

| HWThread | Thread | Core | Socket |

|----------|--------|------|--------|

| 0        | 0      | 0    | 0      |

| 1        | 1      | 0    | 0      |

| 2        | 0      | 1    | 0      |

| 3        | 1      | 1    | 0      |

| 4        | 0      | 2    | 0      |

| 5        | 1      | 2    | 0      |

| 6        | 0      | 3    | 0      |

| 7        | 1      | 3    | 0      |

| 8        | 0      | 0    | 1      |

| 9        | 1      | 0    | 1      |

| 10       | 0      | 1    | 1      |

| 11       | 1      | 1    | 1      |

| 12       | 0      | 2    | 1      |

| 13       | 1      | 2    | 1      |

| 14       | 0      | 3    | 1      |

| 15       | 1      | 3    | 1      |

Slide 73 / 154

# likwid-topology continued

```

Socket 0: ( 0 1 2 3 4 5 6 7 )

Socket 1: ( 8 9 10 11 12 13 14 15 )

*****************

Cache Topology

******************

Level:

32 kB

Size:

Cache groups: (01)(23)(45)(67)(89)(1011)(1213)(1415)

Level:

Size:

256 kB

Cache groups: (01)(23)(45)(67)(89)(1011)(1213)(1415)

Level:

Size:

8 MB

Cache groups: (0 1 2 3 4 5 6 7) (8 9 10 11 12 13 14 15)

```

... and also try the ultra-cool -g option!

# likwid-pin

- Inspired and based on ptoverride (Michael Meier, RRZE) and taskset

- Pins process and threads to specific cores without touching code

- Directly supports pthreads, gcc OpenMP, Intel OpenMP

- Allows user to specify skip mask (i.e., supports many different compiler/MPI combinations)

- Can also be used as replacement for taskset

- Uses logical (contiguous) core numbering when running inside a restricted set of cores

- Supports logical core numbering inside node, socket, core

- Usage examples:

```

- env OMP_NUM_THREADS=6 likwid-pin -t intel -c 0,2,4-6 ./myApp parameters

```

```

- env OMP_NUM_THREADS=6 likwid-pin -c S0:0-2@S1:0-2 ./myApp

```

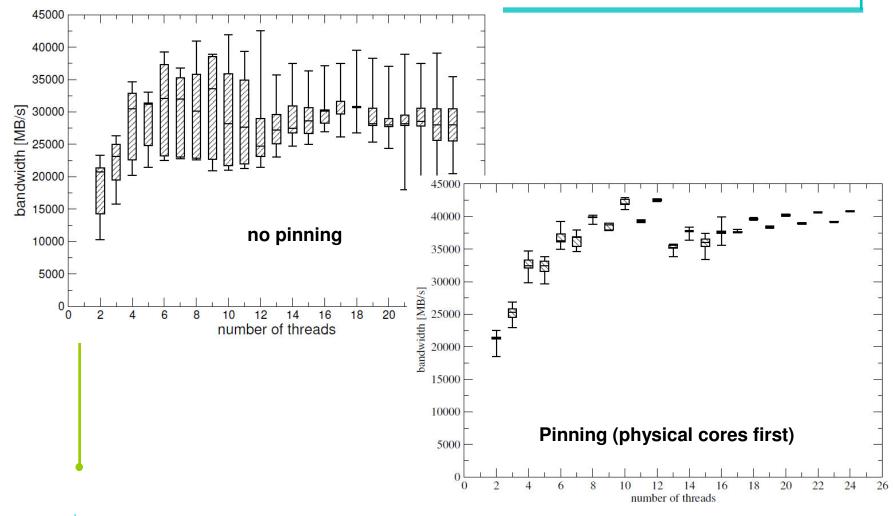

# **Example: STREAM benchmark on 12-core Intel Westmer**

Anarchy vs. thread pinning

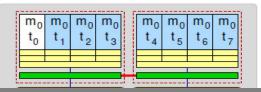

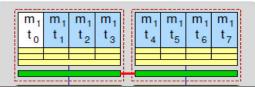

## Topology ("mapping") choices with MPI+OpenMP:

More examples using Intel MPI+compiler & home-grown mpirun

One MPI process per node

One MPI process per socket

```

env OMP_NUM_THREADS=4 mpirun -npernode 2 \

-pin "0,1,2,3_4,5,6,7" ./a.out

```

OpenMP threads pinned "round robin" across cores in node

```

env OMP_NUM_THREADS=4 mpirun -npernode 2 \

-pin "0,1,4,5_2,3,6,7" \

likwid-pin -t intel -c 0,2,1,3 ./a.out

```

Two MPI processes per socket

```

Hybrid Parallel Programming

Slide 77 / 154

```

## MPI/OpenMP hybrid "how-to": Take-home messages

- Do not use hybrid if the pure MPI code scales ok

- Be aware of intranode MPI behavior

- Always observe the topology dependence of

- Intranode MPI

- OpenMP overheads

- Enforce proper thread/process to core binding, using appropriate tools (whatever you use, but use SOMETHING)

- Multi-LD OpenMP processes on ccNUMA nodes require correct page placement

- Finally: Always compare the best pure MPI code with the best OpenMP code!

Rabenseifner, Hager, Jost

### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

#### Mismatch Problems

- Opportunities:

Application categories that can benefit from hybrid parallelization

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

- Other options on clusters of SMP nodes

- Summary

## **Mismatch Problems**

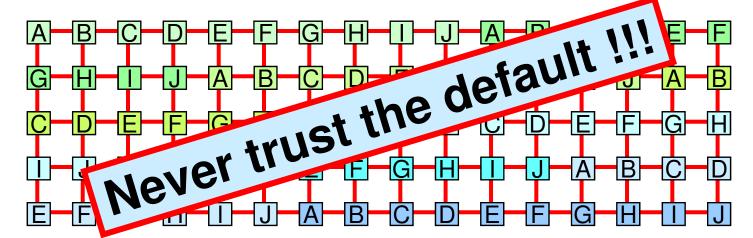

- None of the programming models fits to the hierarchical hardware — (cluster of SMP nodes)

- Several mismatch problems

- → following slides

- Benefit through hybrid programming

- → Opportunities, see next section

- Quantitative implications

- → depends on you application

| Examples:                                 | No.1 | No.2        |

|-------------------------------------------|------|-------------|

| Benefit through hybrid (see next section) | 30%  | 10%         |

| Loss by mismatch problems                 | -10% | <b>-25%</b> |

| Total                                     | +20% | -15%        |

CPU(socket)

SMP board

ccNUMA node

Cluster of ccNUMA/SMP nodes

Core

In most cases:

Both categories!

pure MPI

one MPI process on each core

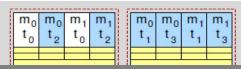

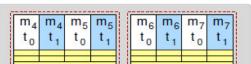

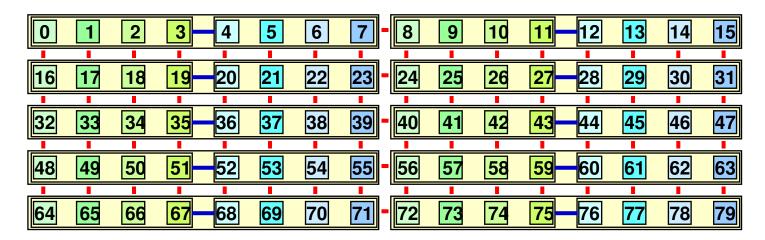

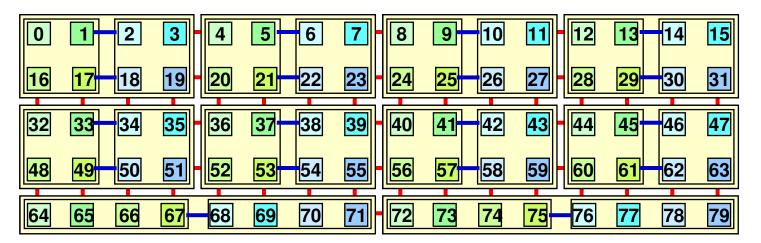

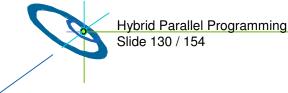

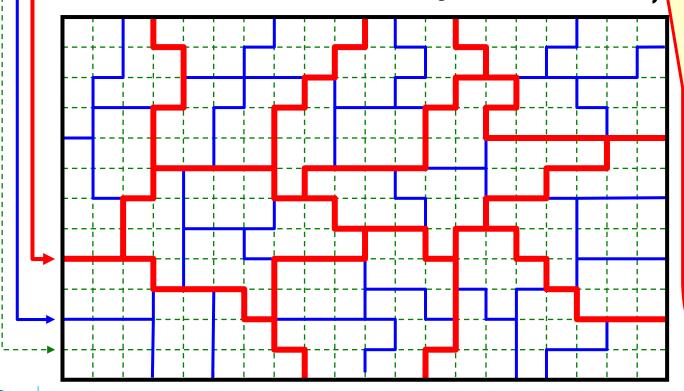

Application example on 80 cores:

- Cartesian application with 5 x 16 = 80 sub-domains

- On system with 10 x dual socket x quad-core

- + 17 x inter-node connections per node

- 1 x inter-socket connection per node

Sequential ranking of MPI\_COMM\_WORLD

Does it matter?

Hybrid Faraner Programming Slide 81 / 154

Rabenseifner, Hager, Jost

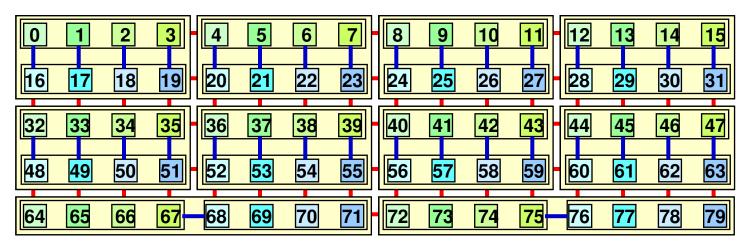

pure MPI one MPI process

on each core

Application example on 80 cores:

- Cartesian application with 5 x 16 = 80 sub-domains

- On system with 10 x dual socket x quad-core

- + 32 x inter-node connections per node

- 0 x inter-socket connection per node

Round robin ranking of MPI\_COMM\_WORLD

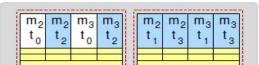

pure MPI

one MPI process on each core

Application example on 80 cores:

- Cartesian application with  $5 \times 16 = 80$  sub-domains

- On system with 10 x dual socket x quad-core

- + 12 x inter-node connections per node

- + 4 x inter-socket connection per node domain decomposition

Two levels of domain decomposition

**Bad** affinity of cores to thread ranks

pure MPI

one MPI process on each core

Application example on 80 cores:

- Cartesian application with 5 x 16 = 80 sub-domains

- On system with 10 x dual socket x quad-core

- + 12 x inter-node connections per node

- + 2 x inter-socket connection per node domain decomposition

Two levels of domain decomposition

Good affinity of cores to thread ranks

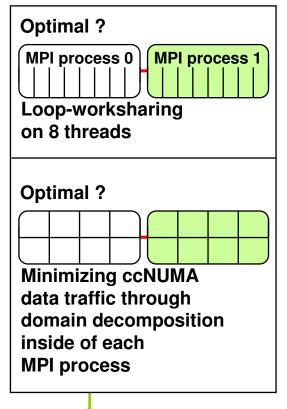

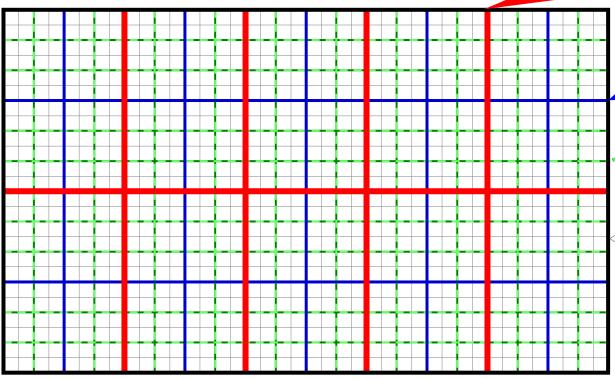

# hybrid MPI+OpenMP

MPI: inter-node communication

OpenMP: inside of each SMP node

Exa.: 2 SMP nodes, 8 cores/node

#### **Problem**

Does application topology inside of SMP parallelization fit on inner hardware topology of each SMP node?

#### Solutions:

- Domain decomposition inside of each thread-parallel MPI process, and

- first touch strategy with OpenMP

### Successful examples:

Multi-Zone NAS Parallel Benchmarks (MZ-NPB)

# hybrid MPI+OpenMP

MPI: inter-node communication OpenMP: inside of each SMP node

#### Application example:

- Same Cartesian application aspect ratio: 5 x 16

- On system with 10 x dual socket x quad-core

- 2 x 5 domain decomposition

- 3 x inter-node connections per node, but ~ 4 x more traffic

- 2 x inter-socket connection per node

Hybrid Parallel Programm Slide 86 / 154

Affinity of cores to thread ranks !!!

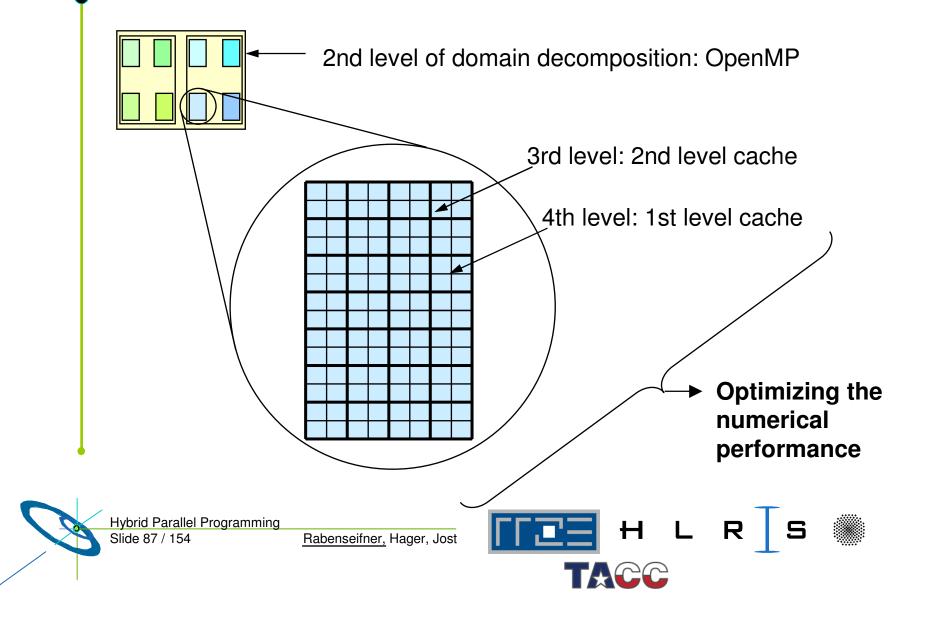

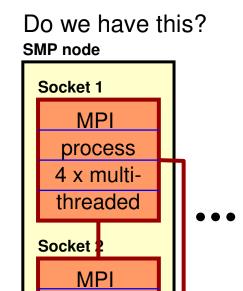

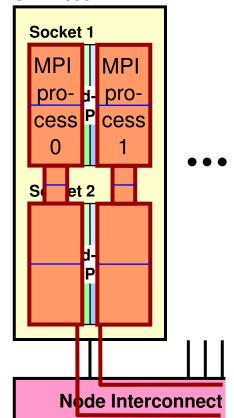

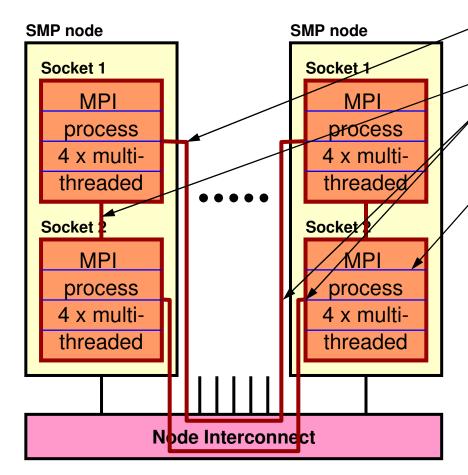

# Numerical Optimization inside of an SMP node

# The Mapping Problem with mixed model

process

4 x multi-

threaded

Node Interconnect

## Several multi-threaded MPI process per SMP node:

#### Problem

Where are your processes and threads really located?

#### Solutions:

- Depends on your platform,

- e.g., with numactl

→ Case study on Sun Constellation Cluster Ranger with BT-MZ and SP-MZ

#### Further questions:

- Where is the NIC¹¹ located?

- Which cores share caches?

# Unnecessary intra-node communication

pure MPI

Mixed model

(several multi-threaded MPI processes per SMP node)

#### Problem:

If several MPI process on each SMP node

unnecessary intra-node communication

#### Solution:

Only one MPI process per SMP node

#### Remarks:

- MPI library must use appropriate fabrics / protocol for intra-node communication

- Intra-node bandwidth higher than inter-node bandwidth

→ problem may be small

- MPI implementation may cause unnecessary data copying

→ waste of memory bandwidth

Quality aspects of the MPI library

# SC10 SC111 NewOrleans, LA Seattle, WA Supposed

# Sleeping threads and network saturation

with

**Masteronly**

MPI only outside of parallel regions

```

for (iteration ....)

{

#pragma omp parallel

numerical code

/*end omp parallel */

/* on master thread only */

MPI_Send (original data

to halo areas

in other SMP nodes)

MPI_Recv (halo data

from the neighbors)

} /*end for loop

```

#### **Problem 1:**

– Can the master thread saturate the network?

#### Solution:

- If not, use mixed model

- i.e., several MPIprocesses per SMP node

#### **Problem 2:**

Sleeping threads are wasting CPU time

#### Solution:

Overlapping of computation and communication

#### Problem 1&2 together:

Producing more idle time through lousy bandwidth of master thread

## **OpenMP: Additional Overhead & Pitfalls**

- Using OpenMP

- → may prohibit compiler optimization

- → may cause significant loss of computational performance

- Thread fork / join overhead

- On ccNUMA SMP nodes:

See, e.g., the necessary **–O4** flag with mpxlf\_r on IBM Power6 systems

- Loss of performance due to missing memory page locality or missing first touch strategy

- E.g. with the masteronly scheme:

- One thread produces data

- Master thread sends the data with MPI

- → data may be internally communicated from one memory to the other one

- Amdahl's law for each level of parallelism

- Using MPI-parallel application libraries? → Are they prepared for hybrid?

## **Overlapping Communication and Computation**

MPI communication by one or a few threads while other threads are computing

#### Three problems:

- the application problem:

- one must separate application into:

- code that can run before the halo data is received

- code that needs halo data

## → very hard to do !!!

- the thread-rank problem:

- comm. / comp. via thread-rank

- cannot use work-sharing directives

- → loss of major **OpenMP support** (see next slide)

- the load balancing problem

```

if (my thread rank < 1) {

MPI Send/Recv....

} else {

my_range = (high-low-1) / (num_threads-1) + 1;

my_low = low + (my_thread_rank+1)*my_range;

my_high=high+ (my_thread_rank+1+1)*my_range;

my high = max(high, my high)

for (i=my low; i<my high; i++) {

```

## **Overlapping Communication and Computation**

MPI communication by one or a few threads while other threads are computing

#### **Subteams**

Important proposal for OpenMP 3.x or OpenMP 4.x

Barbara Chapman et al.: Toward Enhancing OpenMP's Work-Sharing Directives. In proceedings, W.E. Nagel et al. (Eds.): Euro-Par 2006, LNCS 4128, pp. 645-654, 2006.

```

#pragma omp parallel

#pragma omp single onthreads(0)

MPI Send/Recv....

#pragma omp for onthreads( 1 : omp get numthreads()-1 )

for (.....)

{ /* work without halo information */

} /* barrier at the end is only inside of the subteam */

#pragma omp barrier

#pragma omp for

for (.....)

{ /* work based on halo information */

} /*end omp parallel */

```

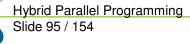

# **Parallel Programming Models on Hybrid Platforms**

pure MPI one MPI process on each core hybrid MPI+OpenMP

MPI: inter-node communication

OpenMP: inside of each SMP node

OpenMP only distributed virtual shared memory

No overlap of Comm. + Comp.

MPI only outside of parallel regions of the numerical application code

Overlapping Comm. + Comp.

MPI communication by one or a few threads while other threads are computing

Masteronly

MPI only outside

of parallel regions

Multiple/only

- appl. threads

- inside of MPI

Funneled

MPI only

on master-thread

Multiple more than one thread may communicate

Different strategies to simplify the load balancing

Funneled & Reserved reserved thread for communication

Funneled

with

Full Load

Balancing

Multiple & Reserved reserved threads for communication

Multiple

with

Full Load

Balancing

Hybrid Parallel Programming Slide 94 / 154

Rabenseifner, Hager, Jost

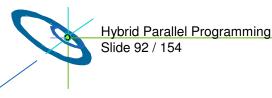

## **Experiment: Matrix-vector-multiply (MVM)**

- Jacobi-Davidson-Solver on IBM SP Power3 nodes with 16 CPUs per node

- funneled&reserved is always faster in this experiments

- Reason:

Memory bandwidth

is already saturated

by 15 CPUs, see inset

- Inset: Speedup on 1 SMP node using different number of threads

Source: R. Rabenseifner, G. Wellein: Communication and Optimization Aspects of Parallel Programming Models on Hybrid Architectures. International Journal of High Performance Computing Applications, Vol. 17, No. 1, 2003, Sage Science Press.

# Overlapping: Using OpenMP tasks

NEW OpenMP Tasking Model gives a new way to achieve more parallelism form hybrid computation.

Alice Koniges et al.:

Application Acceleration on Current and Future Cray Platforms. Proceedings, CUG 2010, Edinburgh, GB, May 24-27, 2010.

# Case study: Communication and Computation in Gyrokinetic Tokamak Simulation (GTS) shift routine

```

!reorder remaining particles: fill holes

NDEPENDENT

do iterations = 1,N

fill_hole(p_array);

!compute particles to be shifted

! send number of particles to move right

!$omp parallel do

MPI SENDRECV(x, length = 2,...);

shift_p=particles_to_shift(p_array);

!send to right and receive from left

27

MPI_SENDRECV(sendright, length=g(x),..)

!communicate amount of shifted

!send number of particles to move left

29

particles and return if equal to 0

MPL SENDRECV(v, length = 2...);

shift p=x+y

send to left and receive from right!

31

MPI ALLREDUCE(shift_p, sum_shift_p)

INDEPENDENT

SEMI-INDEPENDENT

MPI SENDRECV(sendleft, length=g(y),..);

if (sum_shift_p==0) { return; }

33

!adding shifted particles from right

!pack particle to move right and left

!$omp parallel do

35

!$omp parallel do

13

do m=1.x

do m=1.x

p_{array}(h(m)) = sendright(m);

37

15

sendright(m)=p array(f(m));

enddo

enddo

!adding shifted particles from left

39

!$omp parallel do

17

!$omp parallel do

do n=1.v

do n=1,y

41

sendleft(n) = p_array(f(n));

19

p array (h(n)) = sendleft(n);

enddo

43

enddo

GTS shift routine

```

Work on particle array (packing for sending, reordering, adding after sending) can be overlapped with **data independent** MPI communication using **OpenMP tasks**.

## Overlapping can be achieved with OpenMP tasks (1st part)

```

!pack particle to move left

integer stride=1000

do n=1,y-stride, stride

18

2

!$omp parallel

!$omp task

! $omp master

do nn=0, stride -1.1

20

!pack particle to move right

sendleft(n+nn) = p_array(f(n+nn));

do m=1,x-stride, stride

22

enddo

!$omp task

6

!$omp end task

do mm=0, stride -1,1

enddo

24

sendright(m+mm) = p array(f(m+mm));

! Somp task

enddo

26

do n=n, y

!$omp end task

10

sendleft(n) = p_array(f(n));

enddo

28

enddo

!$omp task

12

! Somp end task

MPI_ALLREDUCE(shift_p, sum_shift_p);

do m=m, x

30

sendright(m) = p_array(f(m));

14

! Somp end master

!$omp end parallel

32

enddo

if(sum_shift_p==0) { return; }

!$omp end task

16

```

Overlapping MPI\_Allreduce with particle work

- Overlap: Master thread encounters (!\$omp master) tasking statements and creates work for the thread team for deferred execution. MPI Allreduce call is immediately executed.

- MPI implementation has to support at least MPI\_THREAD\_FUNNELED

- Subdividing tasks into smaller chunks to allow better *load balancing* and *scalability* among threads.

## Overlapping can be achieved with OpenMP tasks (2<sup>nd</sup> part)

```

! $omp parallel

!$omp master

!$omp task

fill_hole(p_array);

! Somp end task

MPI\_SENDRECV(x, length = 2,...);

IMPI SENDRECV (sendright, length=g(x),...);

MPI_SENDRECV(y, length = 2,...

! Somp end master

! Somp end parallel

11

Overlapping particle reordering

```

Particle reordering of remaining particles (above) and adding sent particles into array (right) & sending or receiving of shifted particles can be independently executed.

```

! $omp parallel

! $omp master

2

! adding shifted particles from right

do m=1,x-stride, stride

!$omp task

do mm=0, stride -1.1

6

p_array(h(m)) = sendright(m);

8

!$omp end task

enddo

10

!$omp task

12

do m=m, x

p_array(h(m)) = sendright(m);

enddo

14

!$omp end task

16

MPI_SENDRECV(sendleft,length=g(y),..);

! Somp end master

18

! $omp end parallel

20

! adding shifted particles from left

! $omp parallel do

22

do n=1,v

p_{array}(h(n)) = sendleft(n);

24

enddo

```

Overlapping remaining MPI Sendrecv

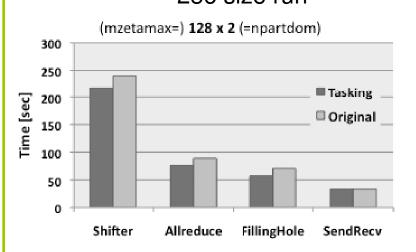

# OpenMP tasking version outperforms original shifter, especially in larger poloidal domains

## 256 size run

#### 2048 size run

- Performance breakdown of GTS shifter routine using 4 OpenMP threads per MPI process with varying domain decomposition and particles per cell on Franklin Cray XT4.

- MPI communication in the shift phase uses a toroidal MPI communicator (constantly 128).

- Large performance differences in the 256 MPI run compared to 2048 MPI run!

- Speed-Up is expected to be higher on larger GTS runs with hundreds of thousands CPUs since MPI communication is more expensive.

# OpenMP/DSM

- Distributed shared memory (DSM) //

- Distributed virtual shared memory (DVSM) //

- Shared virtual memory (SVM)

- Principles

- emulates a shared memory

- on distributed memory hardware

- Implementations

- e.g., Intel<sup>®</sup> Cluster OpenMP

#### Basic idea:

- Between OpenMP barriers, data exchange is not necessary, i.e.,

visibility of data modifications to other threads only after synchronization.

- When a page of sharable memory is not up-to-date, it becomes *protected*.

- Any access then faults (SIGSEGV) into Cluster OpenMP runtime library, which requests info from remote nodes and updates the page.

- Protection is removed from page.

- Instruction causing the fault is re-started, this time successfully accessing the data.

# Comparison: MPI based parallelization ←→ DSM

- MPI based:

- Potential of boundary exchange between two domains in one large message

- → Dominated by **bandwidth** of the network

- DSM based (e.g. Intel<sup>®</sup> Cluster OpenMP):

- Additional latency based overhead in each barrier

- May be marginal

- Communication of updated data of pages

- → Not all of this data may be needed

- → i.e., too much data is transferred

- → Packages may be to small

- → Significant latency

- Communication not oriented on boundaries of a domain decomposition

- probably more data must be transferred than necessary

by rule of thumb:

Communication may be 10 times slower than with MPI

# Comparing results with heat example

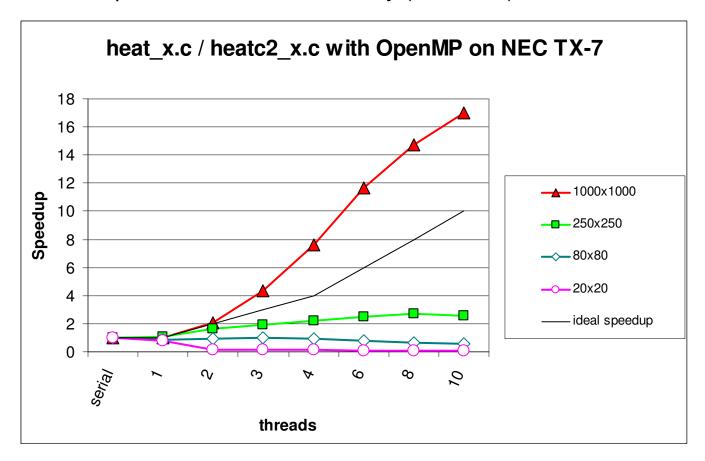

Normal OpenMP on shared memory (ccNUMA) NEC TX-7

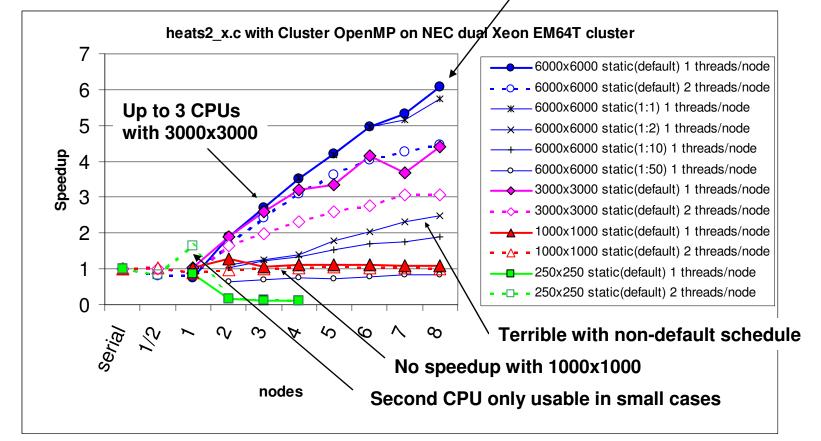

# Heat example: Cluster OpenMP Efficiency

Cluster OpenMP on a Dual-Xeon cluster

Efficiency only with small communication foot-print

## Back to the mixed model - an Example

- Topology-problem solved: Only horizontal inter-node comm.

- Still intra-node communication

- Several threads per SMP node are communicating in parallel:

- → network saturation is possible

- Additional OpenMP overhead

- With Masteronly style: 75% of the threads sleep while master thread communicates

- With Overlapping Comm. & Comp.: Master thread should be reserved for communication only partially – otherwise too expensive

- MPI library must support

- Multiple threads

- Two fabrics (shmem + internode)

### No silver bullet

- The analyzed programming models do **not** fit on hybrid architectures

- whether drawbacks are minor or major

- depends on applications' needs

- But there are major opportunities → next section

- In the NPB-MZ case-studies

- We tried to use optimal parallel environment

- for pure MPI

- for hybrid MPI+OpenMP

- i.e., the developers of the MZ codes and we tried to minimize the mismatch problems

- → the opportunities in next section dominated the comparisons

### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

- Mismatch Problems

- Opportunities: Application categories that can benefit from hybrid parallelization

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

Rabenseifner, Hager, Jost

- Other options on clusters of SMP nodes

- Summary

#### **Nested Parallelism**

- Example NPB: BT-MZ (Block tridiagonal simulated CFD application)

- Outer loop:

- limited number of zones → limited parallelism

- zones with different workload → speedup < Sum of workload of all zones Max workload of a zone

- Inner loop:

- OpenMP parallelized (static schedule)

- Not suitable for distributed memory parallelization

- Principles:

- Limited parallelism on outer level

- Additional inner level of parallelism

- Inner level not suitable for MPI

- Inner level may be suitable for static OpenMP worksharing

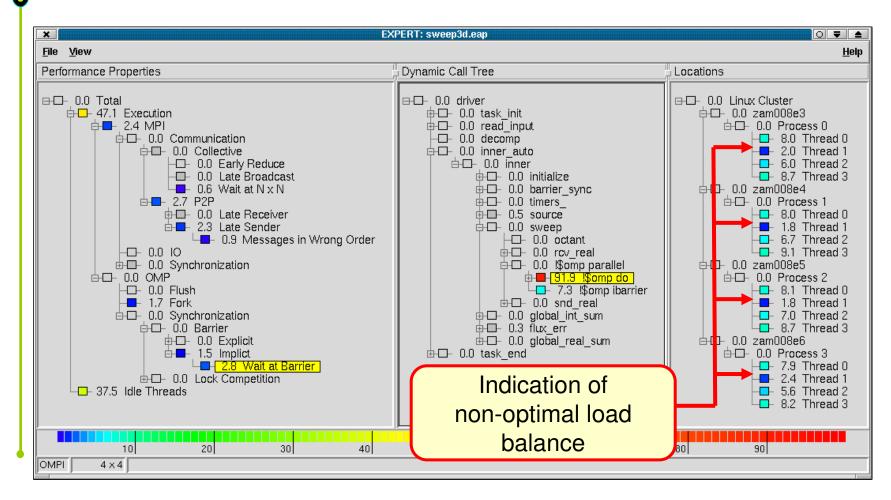

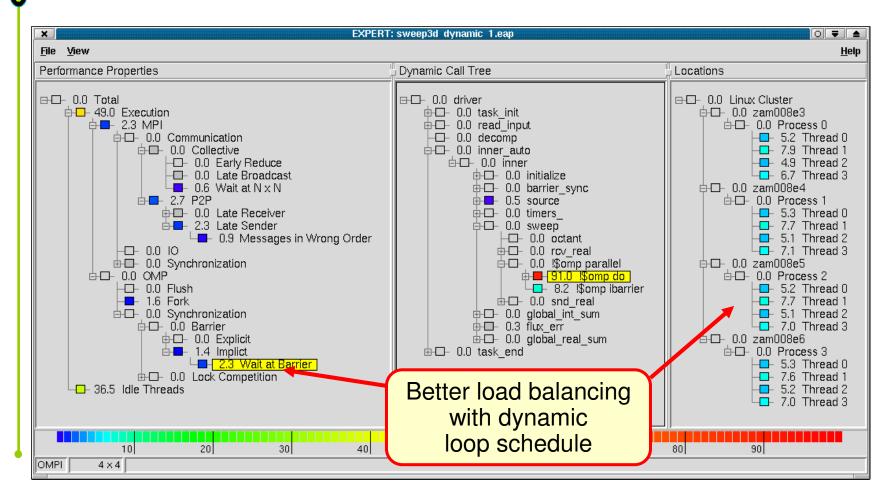

# Load-Balancing (on same or different level of parallelism)

- OpenMP enables

- Cheap dynamic and guided load-balancing

- Just a parallelization option (clause on omp for / do directive)

- Without additional software effort,

- Without explicit data movement

- #pragma omp parallel for schedule(dynamic)

for (i=0; i<n; i++) {</pre>

- /\* poorly balanced iterations \*/ ...

- On MPI level

- Dynamic load balancing requires moving of parts of the data structure through the network

- Significant runtime overhead

- Complicated software / therefore not implemented

#### MPI & OpenMP

Simple static load-balancing on MPI level, dynamic or guided on OpenMP level medium quality cheap implementation

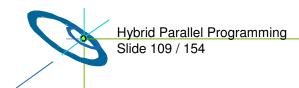

## **Memory consumption**

- Shared nothing

- Heroic theory

- In practice: Some data is duplicated

- MPI & OpenMP

With n threads per MPI process:

Duplicated data may be reduced by factor n

## Case study: MPI+OpenMP memory usage of NPB

Hongzhang Shan, Haoqiang Jin, Karl Fuerlinger, Alice Koniges, Nicholas J. Wright: Analyzing the Effect of Different Programming Models Upon Performance and Memory Usage on Cray XT5 Platorms. Proceedings, CUG 2010, Edinburgh, GB, May 24-27, 2010.

### **Memory consumption (continued)**

- Future:

- With 100+ cores per chip the memory per core is limited.

- Data reduction through usage of shared memory may be a key issue

- Domain decomposition on each hardware level

- Maximizes

- Data locality

- Cache reuse

- Minimizes

- ccNUMA accesses

- Message passing

- No halos between domains inside of SMP node

- Minimizes

- Memory consumption

Rabenseifner, Hager, Jost

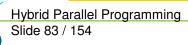

### How many threads per MPI process?

- SMP node = with m sockets and n cores/socket

- How many threads (i.e., cores) per MPI process?

- Too many threads per MPI process

- → overlapping of MPI and computation may be necessary,

- → some NICs unused?

- Too few threads

- → too much memory consumption (see previous slides)

- Optimum

- somewhere between 1 and m x n threads per MPI process,

- Typically:

- Optimum = n, i.e., 1 MPI process per socket

- Sometimes = n/2 i.e., 2 MPI processes per socket

- Seldom = 2n, i.e., each MPI process on 2 sockets

# Opportunities, if MPI speedup is limited due to algorithmic problems

- Algorithmic opportunities due to larger physical domains inside of each MPI process

- → If multigrid algorithm only inside of MPI processes

- → If separate preconditioning inside of MPI nodes and between MPI nodes

- → If MPI domain decomposition is based on physical zones

### To overcome MPI scaling problems

- Reduced number of MPI messages, reduced aggregated message size

- MPI has a few scaling problems

- Handling of more than 10,000 MPI processes

- Irregular Collectives: MPI ....v(), e.g. MPI Gatherv()

- > Scaling applications should not use MPI ....v() routines

- MPI-2.1 Graph topology (MPI Graph create)

- > MPI-2.2 MPI Dist graph create adjacent

- Creation of sub-communicators with MPI Comm create

- > MPI-2.2 introduces a new scaling meaning of MPI Comm create

- ... see P. Balaji, et al.: **MPI on a Million Processors.** Proceedings EuroPVM/MPI 2009.

- Hybrid programming reduces all these problems (due to a smaller number of processes)

# Summary: Opportunities of hybrid parallelization (MPI & OpenMP)

- Nested Parallelism

- → Outer loop with MPI / inner loop with OpenMP

- Load-Balancing

- → Using OpenMP *dynamic* and *guided* worksharing

- Memory consumption

- → Significantly reduction of replicated data on MPI level

- Opportunities, if MPI speedup is limited due to algorithmic problem

- → Significantly reduced number of MPI processes

- Reduced MPI scaling problems

- → Significantly reduced number of MPI processes

#### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

- Mismatch Problems

- Opportunities:

Application categories that can benefit from hybrid parallelization

- Thread-safety quality of MPI libraries

- Tools for debugging and profiling MPI+OpenMP

- Other options on clusters of SMP nodes

- Summary

# MPI rules with OpenMP / Automatic SMP-parallelization

Special MPI-2 Init for multi-threaded MPI processes:

REQUIRED values (increasing order):

MPI\_THREAD\_SINGLE: Only one thread will execute

THREAD\_MASTERONLY: MPI processes may be multi-threaded,

(virtual value, but only master thread will make MPI-calls

not part of the standard) AND only while other threads are sleeping

MPI\_THREAD\_FUNNELED: Only master thread will make MPI-calls

MPI\_THREAD\_SERIALIZED: Multiple threads may make MPI-calls,

but only one at a time

- MPI THREAD MULTIPLE: Multiple threads may call MPI,

with <u>no restrictions</u>

returned provided may be less than REQUIRED by the application

#### Calling MPI inside of OMP MASTER

- Inside of a parallel region, with "OMP MASTER"

- Requires MPI\_THREAD\_FUNNELED,

i.e., only master thread will make MPI-calls

- Caution: There isn't any synchronization with "OMP MASTER"!

Therefore, "OMP BARRIER" normally necessary to guarantee, that data or buffer space from/for other threads is available before/after the MPI call!

```

!$OMP BARRIER

!$OMP MASTER

call MPI_Xxx(...)

!$OMP END MASTER

!$OMP BARRIER

```

#pragma omp barrier

- But this implies that all other threads are sleeping!

- The additional barrier implies also the necessary cache flush!

# ... the barrier is necessary – example with MPI\_Recv

```

!$OMP PARALLEL

!$OMP DO

do i=1,1000

a(i) = buf(i)

end do

!$OMP END DO NOWAIT

!SOMP BARRIER

!SOMP MASTER

call MPI_RECV(buf,...)

!$OMP END MASTER

!SOMP BARRIER

!$OMP DO

do i=1,1000

c(i) = buf(i)

end do

!$OMP END DO NOWAIT

!$OMP END PARALLEL

```

```

#pragma omp parallel

#pragma omp for nowait

for (i=0; i<1000; i++)

a[i] = buf[i];

#pragma omp barrier

#pragma omp master

MPI_Recv(buf,...);

#pragma omp barrier

#pragma omp for nowait

for (i=0; i<1000; i++)

c[i] = buf[i];

/* omp end parallel */

```

## Thread support in MPI libraries

The following MPI libraries offer thread support:

| Implementation | Thread support level                          |  |  |  |  |

|----------------|-----------------------------------------------|--|--|--|--|

| MPlch-1.2.7p1  | Always announces MPI_THREAD_FUNNELED.         |  |  |  |  |

| MPlch2-1.0.8   | ch3:sock supports MPI_THREAD_MULTIPLE         |  |  |  |  |

|                | ch:nemesis has "Initial Thread-support"       |  |  |  |  |

| MPlch2-1.1.0a2 | ch3:nemesis (default) has MPI_THREAD_MULTIPLE |  |  |  |  |

| Intel MPI 3.1  | Full MPI_THREAD_MULTIPLE                      |  |  |  |  |

| SciCortex MPI  | MPI_THREAD_FUNNELED                           |  |  |  |  |

| HP MPI-2.2.7   | Full MPI_THREAD_MULTIPLE (with libmtmpi)      |  |  |  |  |

| SGI MPT-1.14   | Not thread-safe?                              |  |  |  |  |

| IBM MPI        | Full MPI_THREAD_MULTIPLE                      |  |  |  |  |

| Nec MPI/SX     | MPI_THREAD_SERIALIZED                         |  |  |  |  |

Testsuites for thread-safety may still discover bugs in the MPI libraries

Rabenseifner, Hager, Jost

### Thread support within Open MPI

In order to enable thread support in Open MPI, configure with:

configure --enable-mpi-threads

- This turns on:

- Support for full MPI\_THREAD\_MULTIPLE

- internal checks when run with threads (--enable-debug)

configure --enable-mpi-threads --enable-progress-threads

- This (additionally) turns on:

- Progress threads to asynchronously transfer/receive data per network BTI

- Additional Feature:

- Compiling with debugging support, but without threads will check for recursive locking

#### **Outline**

- Introduction / Motivation

- Programming models on clusters of SMP nodes

- Case Studies / pure MPI vs hybrid MPI+OpenMP

- Practical "How-To" on hybrid programming

- Mismatch Problems

- Opportunities: