## Topology aware Cartesian grid mapping with MPI

Christoph Niethammer, Rolf Rabenseifner

High Performance Computing Center Stuttgart, University of Stuttgart, Germany {niethammer,rabenseifner}@hlrs.de

For further information, see https://fs.hlrs.de/projects/par/mpi/EuroMPI2018-Cartesian/ Poster at EuroMPI 2018, Barcelona, Spain, Sep 23-26, 2018

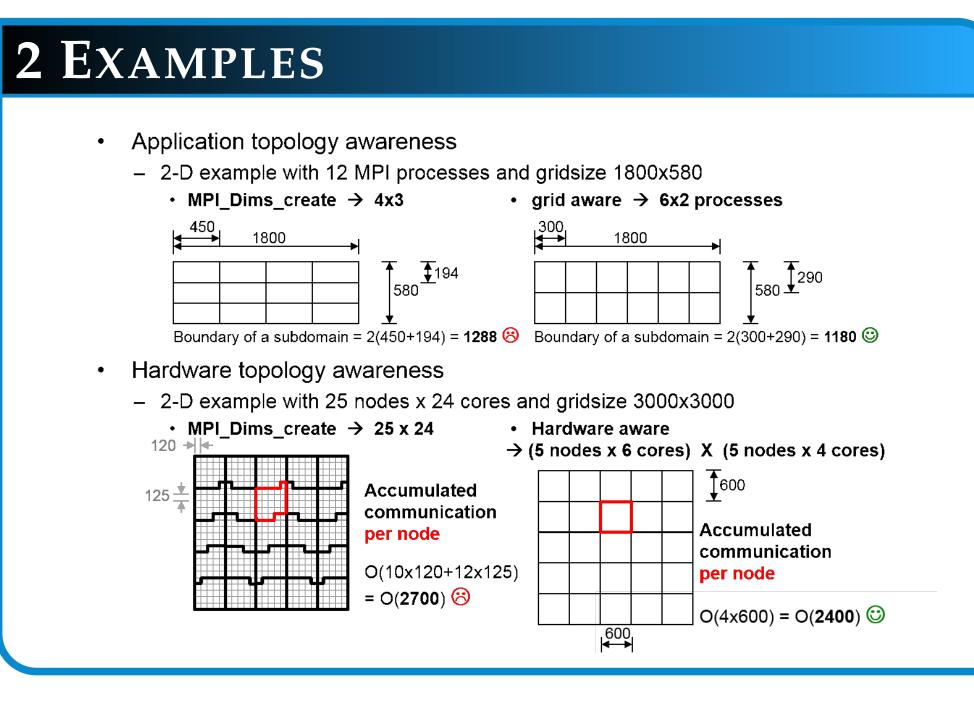

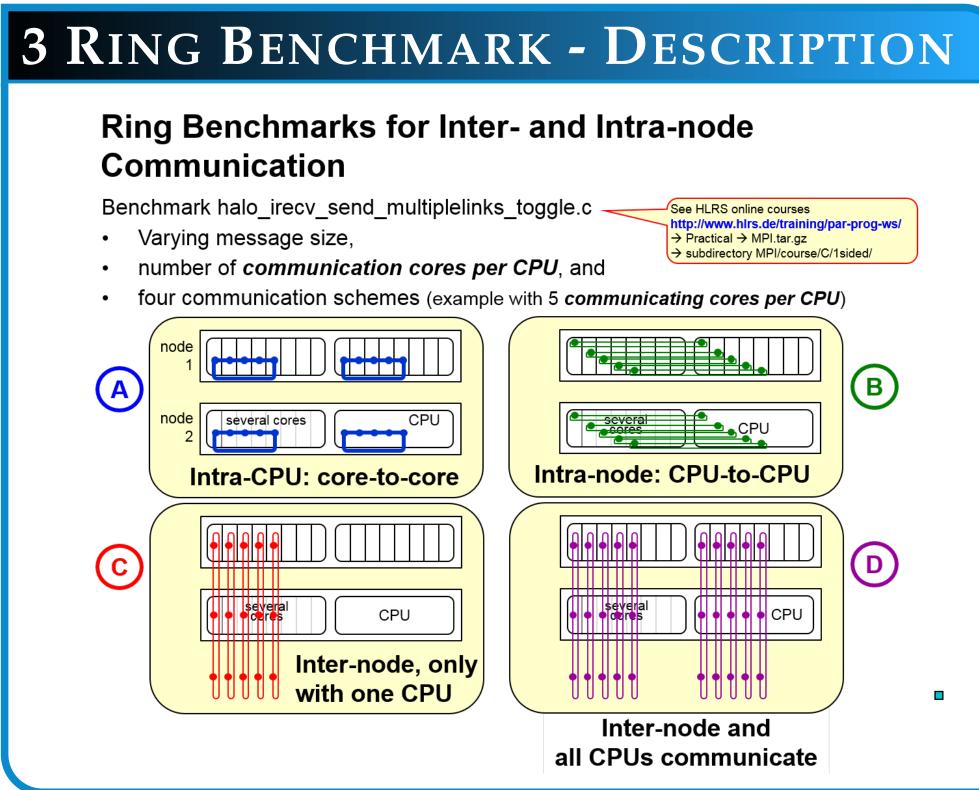

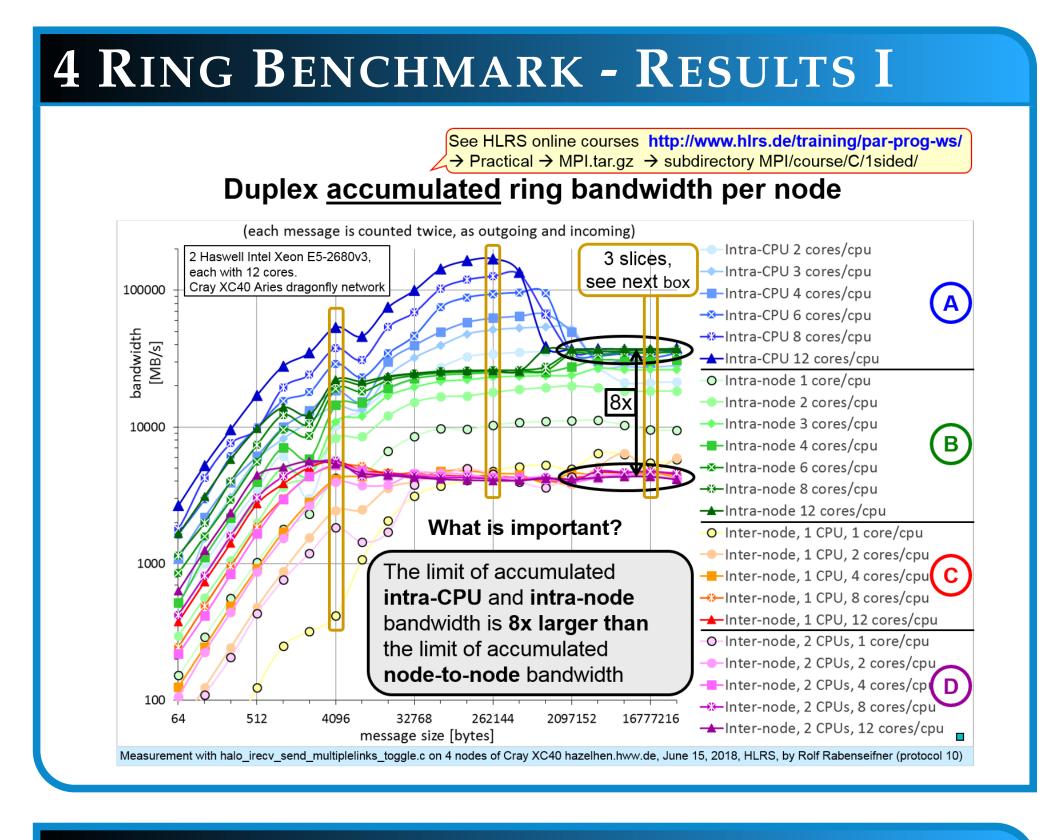

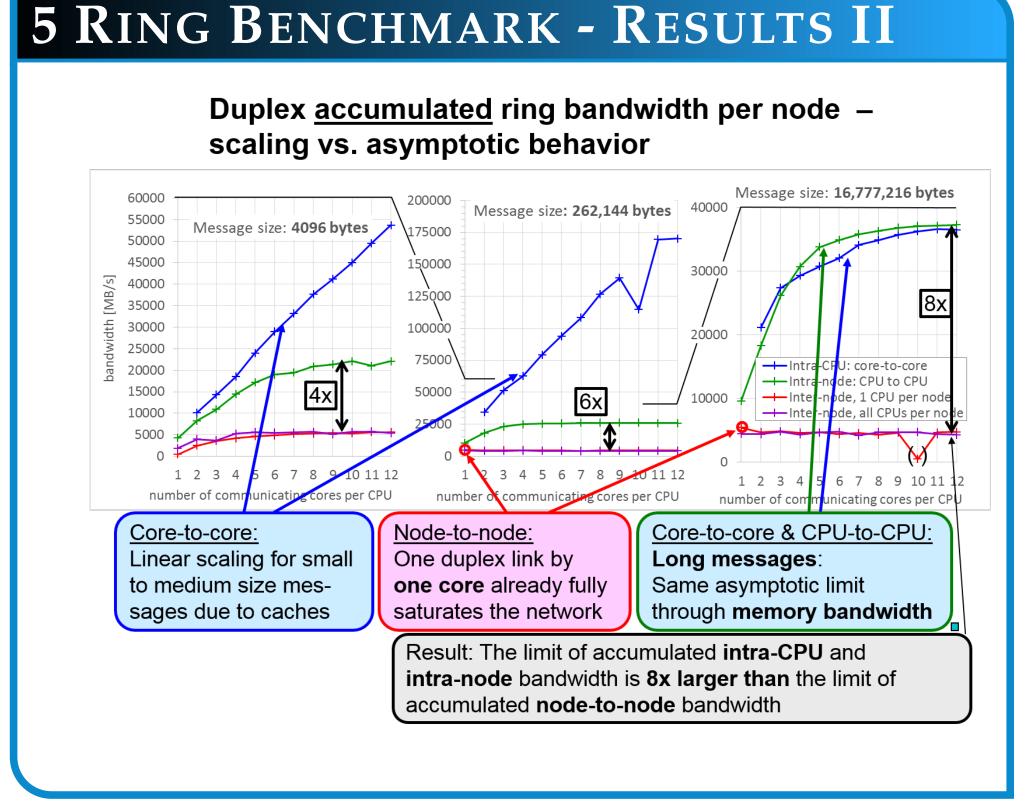

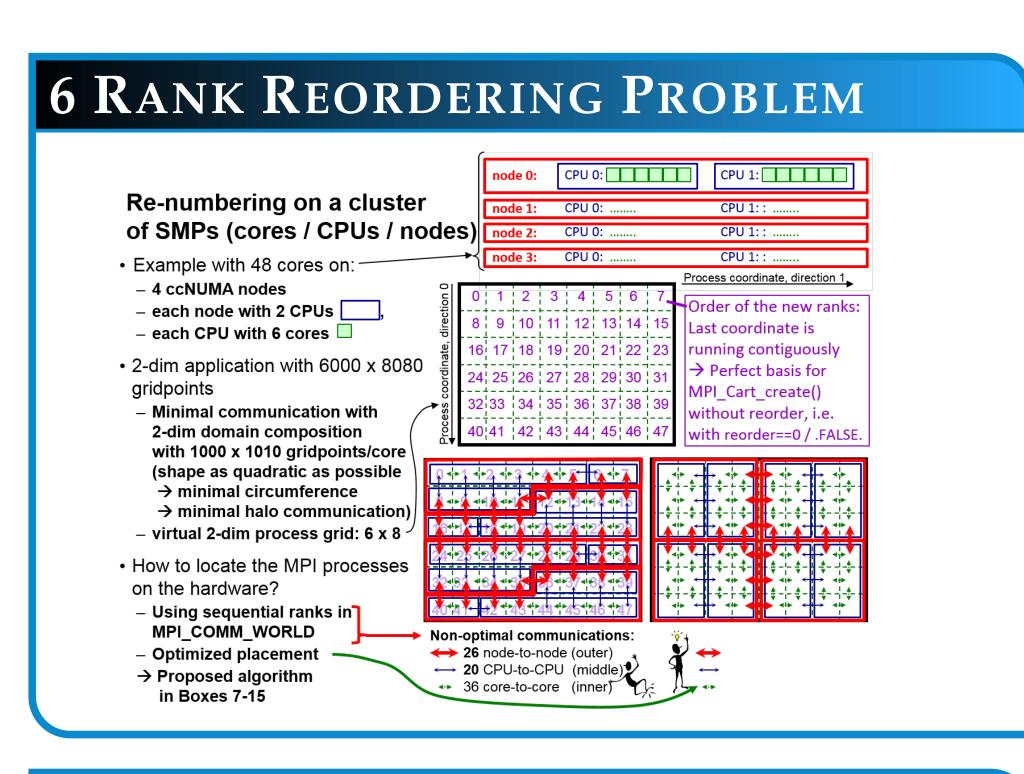

#### 1 ADRESSED PROBLEM The Problems of MPI\_Dims\_create + MPI\_Cart\_create The factorization of a given amount of MPI processes must be Application topology aware [1] Boxes 1+2 Hardware topology aware Current definition of MPI\_Dims\_create is not prepared for this Extreme differences in latency and accumulated bandwidth Boxes 3-5 between inter-node and intra-node communication The reordering by MPI\_Cart\_create: Many implementations do nothing - Box 6 A perfect reordering may require complex domain decomposition algorithms (e.g. Metis) [2] We propose a new and fast algorithm, Boxes 7-15 which is application and hardware topology aware

[1, 2] see References in last box

} Box 17

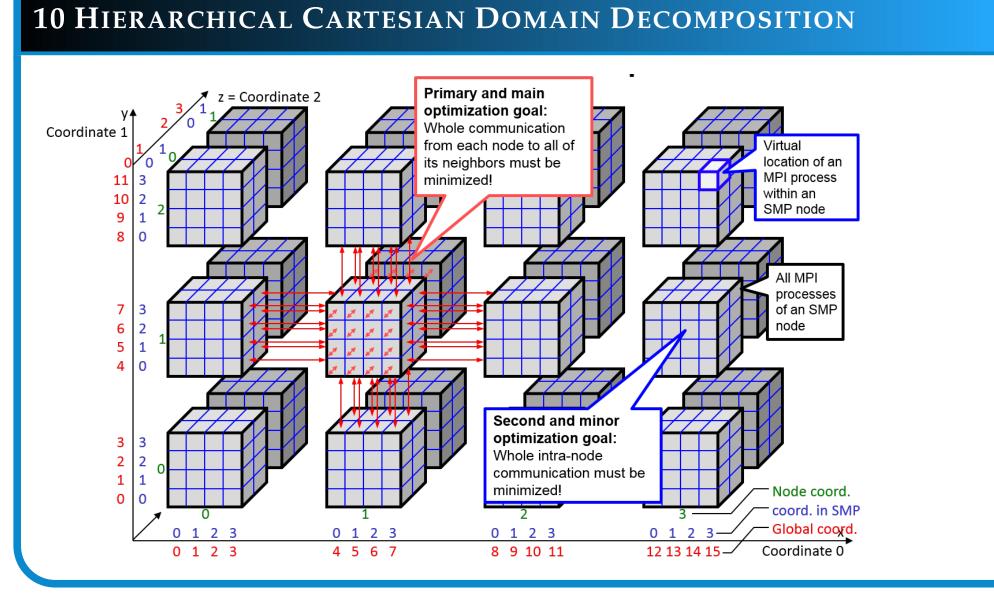

## 7 PROPOSED MAPPING ALGORITHM

- To keep the algorithm small (and fast):

- Use multi-level Cartesian subdomains

- Based on the benchmark results:

- The first and major optimization goal is minimizing the inter-node communication volume

- Using the algorithm from [4] for the multi-dimensional factorization of the number of nodes, but with a modified optimization goal that is application topology aware

- Using the same principles for each further hardware level to minimize

- intra-node (i.e., CPU-to-CPU) communication

- intra-CPU (i.e., core-to-core) communication

## 8 THE OPTIMIZATION ALGORITHM

Given: d-dimensional Cartesian grid with a total of  $T = \prod_{i=1}^{d} t_i$  elements

Level 1 (= outer level = node level) on *N* nodes:

Factorization of N into factors  $(n_i)_{i=1,d}$  with  $N = \prod_{i=1}^d n_i$ Communication cost in both directions

of each dimension (example for d = 3):

$2\frac{t_2t_3}{n_2n_3}$ ,  $2\frac{t_1t_3}{n_1n_3}$ ,  $2\frac{t_1t_2}{n_1n_2}$ • Minimizing the communication costs *c*

$c^{(level=1)} = 2\sum_{i=1}^{d} \prod_{\substack{j=1\\i \neq i}}^{d} \frac{t_j}{n_j} = 2\frac{T}{N}\sum_{i=1}^{d} \frac{n_i}{t_i}$

Summary of Level 1: One must search factors  $(n_i)_{i=1,d}$ - that factorize N with  $N = \prod_{i=1}^{d} n_i$ - and minimize the term  $\sum_{i=1}^{d} \frac{n_i}{t}$

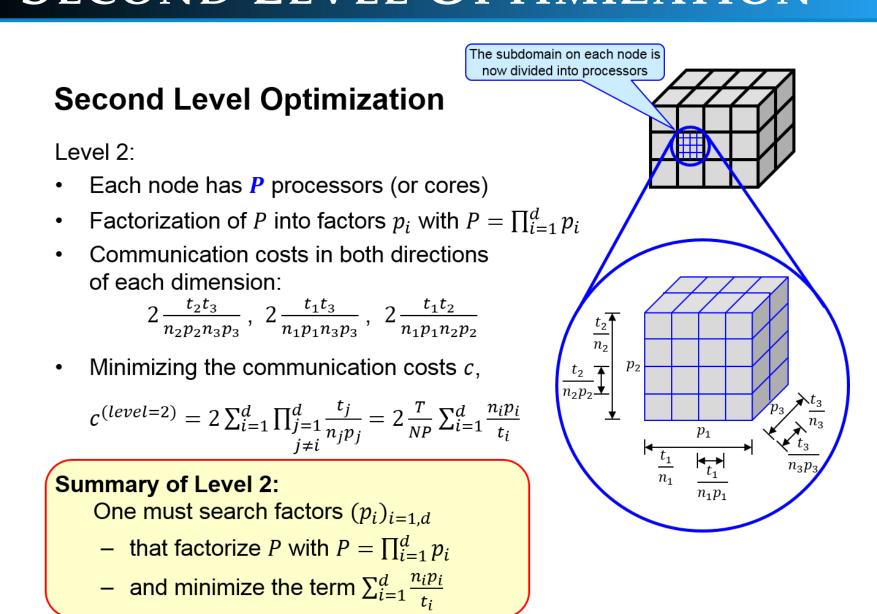

## 9 SECOND LEVEL OPTIMIZATION

## 11 EXAMPLE

- Given: d=3 dimensions, N=625 nodes, P=24 cores, and all  $t_i$  are identical

- Level 1:

- $\rightarrow$  in all formulas, the  $1/t_i$  can be ignored

- Search  $(n_i)_{i=1,3}$  that  $n_1n_2n_3=625$  and  $\sum_{i=1}^3 n_i$  minimal - Result:  $(n_i)_{i=1,3} = (25,5,5)$  with  $\sum_{i=1}^{3} n_i = 35$

- Level 2:

- Search  $(p_i)_{i=1,3}$  that  $p_1p_2p_3=24$  and  $\sum_{i=1}^3 n_ip_i$  minimal - Result:  $(p_i)_{i=1,3} = (1,6,4)$  with  $\sum_{i=1}^{3} n_i p_i = 25 + 30 + 20 = 75$

### Optimized result:

- with (nodes x cores) in each dimension:  $(25x1) \times (5x6) \times (5x4)$

- Total core numbers as used for MPI\_Cart\_create: 25 X 30 X 20 Comparison with existing MPI\_Dims\_create:

- MPI Dims create would result in 25 x 25 x 24 → complex mapping to the hardware is needed, see also slide 3, or no reordering is done  $\rightarrow$  (25x1) X (25x1) X (1x24)

with  $\sum_{i=1}^{3} n_i = 51$  (instead of 35 ©),  $\rightarrow$  46% more inter-node communication!

#### 12 GENERALIZED MULTI-LEVEL OPTIMIZATION

**Given:** d-dimensional Cartesian grid with a total of  $T = \prod_{i=1}^{d} t_i$  elements Number of hardware levels L

and for each level the number of processors  $N^{(l)}$ , l = 1, L

Communication costs on each level *l*:

$$c^{(l)} = 2 \frac{T}{\prod_{k=1}^{l} N^{(k)}} \sum_{i=1}^{d} \frac{\prod_{k=1}^{l} n_i^{(k)}}{t_i} \quad \text{for a factorization } N^{(l)} = \prod_{i=1}^{d} n_i^{(l)}$$

Search:

- On each level l=1..L, one must search a factorization  $\left(n_i^{(l)}\right)_{i=1,d}$  of  $N^{(l)}$

- with  $N^{(l)} = \prod_{i=1}^{d} n_i^{(l)}$

- and minimal sum  $\sum_{i=1}^{d} \frac{\prod_{k=1}^{l} n_i^{(k)}}{t_i}$ ,

i.e., with minimal sum  $\sum_{i=1}^{d} a_i^{(l)} n_i^{(l)}$  with  $a_i^{(l)} = \frac{\prod_{k=1}^{l-1} n_i^{(k)}}{t_i}$

#### 13 WEIGHTED COMMUNICATION VOLUMES

#### Generalization with weighted communication in each direction, e.g. by different halo width

- If the communication cost in each direction i = 1.dis multiplied with a halo width  $w_i$ , e.g.,  $2\frac{t_2t_3}{n_2n_3}w_1$

- On each l = 1...L, the sum to be minimized is

- i.e.,  $\sum_{i=1}^{d} a_i^{(l)} n_i^{(l)}$  with  $a_i^{(l)} = \frac{\prod_{k=1}^{l-1} n_i^{(k)}}{(t_i/w_i)}$

reciprocal values.

highest to smallest.

Loop over divisors from

recursively over i = 1, d,

• Start value for  $n_{i+1}$  is next

MPI\_COMM\_TYPE\_SHARED

MPI COMM TYPE NUMA }

.g., 3 dimensions with a data

grid with 1000 x 1100 x 950

#### 14 USING WEIGHTED MPI\_DIMS\_CREATE

- <u>Task:</u> In general, on each hardware topology level l with l = 1, L and for given  $N^{(l)}$ , find factorizations  $\left(n_i^{(l)}\right)_{i=1,d}$  with  $N^{(l)}=\prod_{i=1}^d n_i^{(l)}$  and

- the following sum is minimal:  $\sum_{i=1}^{d} a_i^{(l)} n_i^{(l)}$  with  $a_i^{(l)} = \frac{\prod_{k=1}^{l-1} n_i^{(k)}}{(t_i/w_i)}$ Algorithm on each level l = 1..L

- Sorting indexes i = 1..d so that the  $(a_{i'})_{i'=1..d}$  to be non-decreasing

- Calculate all divisors of  $N^{(l)}$  i.e. with  $n_i \ge n_{i+1}$ Loop over all non-increasing factorizations and find optimum according to

- 1st criterion: a factorization is better if  $\sum_{i=1}^{d} a_i^{(l)} n_i^{(l)}$  is smaller Additional tricks: • 2<sup>nd</sup> criterion: if the  $\sum_{i=1}^{d} a_i^{(l)} n_i^{(l)}$  is the same then Calculate divisors only upto sqrt(N), calculate the rest by a factorization is better if  $\Delta = n_1^{(l)} - n_d^{(l)}$  is smaller

- 3<sup>rd</sup> criterion: if  $\sum_{i=1}^d n_i$  and  $\Delta = n_1^{(l)} n_d^{(l)}$  are the same then a factorization is better if  $n_{\mathbf{1}}^{(l)}$  is smaller

- Revert the index mapping  $\left(n_{i'}^{(l)}\right)_{i'=1..d}$   $\rightarrow$   $\left(n_{i}^{(l)}\right)_{i=1..d}$

- real divisor equal or smaller Re-mapping of all process ranks according to  $\left(n_i^{(l)}\right)_{i=1..d,l=1,L}$

and creation of the new Cartesian communicator according to algorithm in [2]

# 15 PROPOSED INTERFACE

25\*25\*24 = **15000** processes on 625 ccNUMA nodes with 2 CPUs/node and 12 cores/CPU MPI\_Cart\_ml\_create\_from\_types ( MPI\_Comm comm\_old, int type\_levels[ntype\_levels], int ntype\_levels, double dim weights[ndims] int ndims, int periods[ndims], MPI Info info. MPI\_Comm\_\*comm\_cart ) int dims[ndims]. Rank mapping is based on:

elements -> dim\_weights[] = { 1.0/1000, 1.0/1100, 1.0/950 } The Cartesian communicator reflects this result: 30 x 25 x 20 Node level: **625**= 5 x 25 x 5 CPU level: **2**= 2 x 1 x <sup>2</sup> MPI\_Comm\_rank ( comm\_cart, &my\_rank ); Core level: 12= 3 x 1 x 4 MPI\_Cart\_coords ( comm\_cart, my\_rank, ndims, coords) Result (product): 30 x 25 x 20

e.g., level\_comms[0] is comm\_old, level\_comms MPI Cart\_ml\_create\_from\_comms (int nlevels, and 2) are the result recursively called MPI MPI\_Comm level\_comms[nlevels], Comm\_split\_type with the type\_levels from above. int ndims, double dim\_weights[ndims], int periods[ndims], MPI\_Info info, /\*OUT\*/ int dims[ndims], MPI\_Comm \*comm\_cart ); Same as above

MPI\_Dims\_weighted\_create (int nnodes, int ndims, double dim\_weights[ndims], /\*OUT\*/ int dims[ndims] );

MPI\_Dims\_mI\_create (intinnodes, int ndims, double dim\_weights[ndims], int nlevels, int sizes[nlevels], /\*OUT\*/ int dims\_m/[ndims][nlevels] > above

## 16 CONCLUSION AND OUTLOOK

### Conclusions

- We developed a new algorithm to minimize the total communication time in a cluster of ccNUMA nodes with multi-core CPUs.

- It is needed, due to the significant bandwidth differences between inter- and intra-node communication.

- It can be implemented based on the algorithm in [4], but with a modified optimization goal, and repeated for each hardware level

### Outlook

- We plan to provide a portable implementation, and

- compare it with existing solutions with MPI\_Dims\_create + MPI Cart create.

- We plan to propose an appropriate interface for the next MPI

- standard, because MPI libraries may internally have faster access to the hardware topology information for a given communicator.

## 17 REFERENCES

- [1] Pavan Balaji et al. 2009-2012. Topology awareness in MPI Dims create. https://github.com/mpi-forum/mpi-forumhistoric/issues/195 Accessed 2018-07-19.

- [2] Bill Gropp. 2018. Using Node Information to Implement MPI Cartesian Topologies. In Proceedings of the 25nd European MPI Users' Group Meeting (EuroMPI '18), September 23–26, 2018, Barcelona, Spain. ACM, New York, NY, USA, 9 pages.

- [3] T. Hoefler and M. Snir. 2011. Generic Topology Mapping Strategies for Large-scale Parallel Architectures. In Proceedings of the 2011 ACM International Conference on Supercomputing (ICS'11). ACM, 75–85.

- [4] Jesper Larsson Träff and Felix Donatus Lübbe. 2015. Specification Guideline Violations by MPI Dims Create. In Proceedings of the 22nd European MPI Users' Group Meeting (EuroMPI '15). ACM, New York, NY, USA, Article 19, 2 pages.